Va de Retro DRAM tester [v2.00]

Moderadores: cacharreo, Fundadores

Reglas del Foro

Aquí solo tienen cabida proyectos de hardware que incluyan siempre al menos sus esquemáticos para poder reproducirlos si llevan componentes electrónicos, y si es posible los ficheros del programa en que se hacen, los diseños de las placas, los gerber, etc. Si llevan algún tipo de software asociado debe estar diponible el código fuente

Para los que no cumplen estas condiciones se debe postear en el foro de proyectos generales.

Aquí solo tienen cabida proyectos de hardware que incluyan siempre al menos sus esquemáticos para poder reproducirlos si llevan componentes electrónicos, y si es posible los ficheros del programa en que se hacen, los diseños de las placas, los gerber, etc. Si llevan algún tipo de software asociado debe estar diponible el código fuente

Para los que no cumplen estas condiciones se debe postear en el foro de proyectos generales.

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Va de Retro RAM tester 2.00

Muchas gracias. Tenía la intención de hacer también otro vídeo usando con una pantalla de 0.96" bicolor pero la única que tenía con la polaridad correcta, no funciona a saber por qué.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Va de Retro RAM tester 2.00

El procedimiento para la prueba es ligeramente diferente, simplificando quedaría en, sin Nano, ni pantalla, ni U3, ni U4,...

- comprobar la ausencia de corto en J2#4 y J2#3,

- comprobar que con +5V en J2#4 y J2#3 que no hay consumo, y

- conectar +5V entre J2#3 (GND) y el pin #1 (+5V) del zócalo de U4 y ajustar el potenciómetro (RV1) del conversor DC-DC (HW-668) a +12V.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Va de Retro RAM tester 2.00

Tester 2.00 fw0.27BETA3 y la KM4164B-15 @issalig#A:

(click para ampliar)

Resumen:

00:00 Prueba de la botonera externa moviéndose al tuntún por la lista de opciones

00:22 Test 4164 con J4 en vacío (para provocar el error en la pantalla de cableado)

00:32 Test 4164 con +5V en J4#8 (que con el cableado correcto va bien)

01:03 Test 4164 con +5V en J4#8 y con ZIF#15 conectado a tierra (anulando A4 para provocar un error en el decodificador de direcciones)

01:13 Test 4164 con +5V en J4#8 (que sin el puente en A4 va bien)

(click para ampliar)

Resumen:

00:00 Prueba de la botonera externa moviéndose al tuntún por la lista de opciones

00:22 Test 4164 con J4 en vacío (para provocar el error en la pantalla de cableado)

00:32 Test 4164 con +5V en J4#8 (que con el cableado correcto va bien)

01:03 Test 4164 con +5V en J4#8 y con ZIF#15 conectado a tierra (anulando A4 para provocar un error en el decodificador de direcciones)

01:13 Test 4164 con +5V en J4#8 (que sin el puente en A4 va bien)

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Firmware fw0.27

Firmware fw0.27

Nueva versión recomendada (stable) idéntica a la fw0.27β8.

Funcionamiento

- Logo

- Selección de chip (asegurarse de que el zócalo ZIF está vacío y no hay cables en J4)

- Información sobre el cableado de tensiones ("wiring") entre J3 y J4 (se debe fijar como se indica y, una vez hecho y verificado, colocar el chip en el zócalo ZIF)

- Hay dos modos dependiendo de si se pulsa el botón OK(✓) con:

- Test de pines (Pin test en el que el usuario puede utilizar J3 y un cable conectado a J2/GND (o al pin 20 del zócalo ZIF) para hacer conexiones a los pines 1-19 de J4 y comprobar su lectura en la pantalla, se acaba al pulsar simultáneamente UP(◀) y OK(✓))

- Autodiagnóstico (Self-test), diagnóstico de las conexiones (excepto en J4#9, 10 y 11) en el que solo es necesario seguir las indicaciones que el tester muestra en la esquina inferior izquierda y pulsar el botón OK(✓) para confirmar.

Cambios

- Control completo de Vcc para la placa v2.00 y posteriores.

- En estas nuevas placas Vcc se desconecta nada más reiniciar el Nano.

- Lectura de pulsaciones largas de botones deshabilitada allí donde no hace falta.

- Limitación a 4 cifras en los contadores del test en bucle.

- Salida serie completa habilitada en memorias con modelos 0 y 1.

- Habilitada la comprobación de cableado.

- Habilitado la comprobación del decodificador de direcciones.

- Permite cambiar del test normal al test en bucle.

- Se impide pasar directamente del menú al test obligando a parar en la pantalla de cableado.

- El mensaje de error en el cableado añade la configuración correcta del cableado y detiene el test en bucle.

- El mensaje de error en el decodificador de direcciones interrumpe el test en bucle.

Notas

Nueva versión recomendada (stable) idéntica a la fw0.27β8.

Funcionamiento

- Logo

- Selección de chip (asegurarse de que el zócalo ZIF está vacío y no hay cables en J4)

- Información sobre el cableado de tensiones ("wiring") entre J3 y J4 (se debe fijar como se indica y, una vez hecho y verificado, colocar el chip en el zócalo ZIF)

- Hay dos modos dependiendo de si se pulsa el botón OK(✓) con:

- pulsación corta, test simple que al concluir muestra el resultado (una vez acaban las pruebas sobre la memoria se puede abandonar con el botón BACK(↲) o repetir el test pulsando el botón AGAIN (↺)),

- pulsación larga, test automático que repite una y otra vez las pruebas sobre la memoria y a través del puerto serie facilita la información sobre el número de tests pasados, fallidos, totales además de información detallada en caso de fallo del test (cada vez que acaban las pruebas se puede abandonar dejando pulsado el botón BACK(↲)).

- Test de pines (Pin test en el que el usuario puede utilizar J3 y un cable conectado a J2/GND (o al pin 20 del zócalo ZIF) para hacer conexiones a los pines 1-19 de J4 y comprobar su lectura en la pantalla, se acaba al pulsar simultáneamente UP(◀) y OK(✓))

- Autodiagnóstico (Self-test), diagnóstico de las conexiones (excepto en J4#9, 10 y 11) en el que solo es necesario seguir las indicaciones que el tester muestra en la esquina inferior izquierda y pulsar el botón OK(✓) para confirmar.

Cambios

- Control completo de Vcc para la placa v2.00 y posteriores.

- En estas nuevas placas Vcc se desconecta nada más reiniciar el Nano.

- Lectura de pulsaciones largas de botones deshabilitada allí donde no hace falta.

- Limitación a 4 cifras en los contadores del test en bucle.

- Salida serie completa habilitada en memorias con modelos 0 y 1.

- Habilitada la comprobación de cableado.

- Habilitado la comprobación del decodificador de direcciones.

- Permite cambiar del test normal al test en bucle.

- Se impide pasar directamente del menú al test obligando a parar en la pantalla de cableado.

- El mensaje de error en el cableado añade la configuración correcta del cableado y detiene el test en bucle.

- El mensaje de error en el decodificador de direcciones interrumpe el test en bucle.

Notas

- Para actualizar el firmware o ejecutar cualquiera de los tests siempre hay que tener la precaución de no tener cables en J4 y el zócalo ZIF sin chip (vacío) pues en caso contrario puede producirse un error de comunicación con el Nano.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Firmware fw0.28β1

Se acaba de publicar una nueva versión del firmware, la fw0.28β1 que agrega a las memorias existentes la nueva 4516 que servirá de representante para comprobar DRAM de tipo NMOS como la Intel 2118, la Mostek MK4516, la Hitachi HM4816, las Kyrillisch K565PY6 y K565RU6, la Fujitsu MB8118 y las Motorola MCM4516 y MCM4517.

La nueva tabla de asignación de pines que incluye esta nueva memoria queda como sigue:

Tester 2.00 fw0.28BETA1, la KM4164B-15 @issalig#A corriendo el test 4516.

(click para ampliar)

La nueva tabla de asignación de pines que incluye esta nueva memoria queda como sigue:

Tester 2.00 fw0.28BETA1, la KM4164B-15 @issalig#A corriendo el test 4516.

(click para ampliar)

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Va de Retro RAM tester 2.00

Para crear un entorno de prueba de las plaquitas con el PCA9536D solo se necesita:

- Una pinza (clip) SOIC-8 (la que viene con los accesorios del TL866IIplus),

- 2 resistencias de 10kΩ 1/4W (la resistencia de 10kΩ, el santo grial de la electrónica), y

- 5 cables de breadboard (de pin redondo).

El procedimiento es el siguiente:

1. Crear dos pull-ups en las señales SCL y SDA para compensar la longitud del cable de la pinza SOIC-8.

1.1 Se conectan las dos resistencias de 10kΩ juntas al pin #1 (VCC) de J1',

1.2 el terminal libre de una de las resistencias se conecta al pin #3 (SCK) de J1', y

1.3 el terminal libre de la otra resistencia se conecta al pin #4 (SDA) de J1'.

2. se conectan los 5 cables de breadboard siguiendo esta tabla:

3. Se fija la pinza a la plaquita teniendo cuidado de que quede a ras de la placa y con el pin #1 en su posición.

Y así se pueden probar rápidamente muchas muchas plaquitas con solo cambiar la pinza a otra nueva.

- Una pinza (clip) SOIC-8 (la que viene con los accesorios del TL866IIplus),

- 2 resistencias de 10kΩ 1/4W (la resistencia de 10kΩ, el santo grial de la electrónica), y

- 5 cables de breadboard (de pin redondo).

El procedimiento es el siguiente:

1. Crear dos pull-ups en las señales SCL y SDA para compensar la longitud del cable de la pinza SOIC-8.

1.1 Se conectan las dos resistencias de 10kΩ juntas al pin #1 (VCC) de J1',

1.2 el terminal libre de una de las resistencias se conecta al pin #3 (SCK) de J1', y

1.3 el terminal libre de la otra resistencia se conecta al pin #4 (SDA) de J1'.

2. se conectan los 5 cables de breadboard siguiendo esta tabla:

| Cable | Zócalo DIP-8/Pinza SOIC-8 | Nombre |

|---|---|---|

| Amarillo | Pin 1 | P0 |

| Negro | Pin 4 | GND |

| Azul | Pin 6 | SCL |

| Verde | Pin 7 | SDA |

| Rojo | Pin 8 | VCC |

Y así se pueden probar rápidamente muchas muchas plaquitas con solo cambiar la pinza a otra nueva.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Re: Va de Retro DRAM tester [Completado]

Se ha actualizado la última placa a la versión 2.00a que incluye las modificaciones que hemos comentado al hilo del montaje de la versión 2.00.

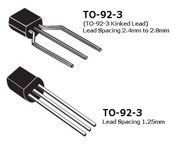

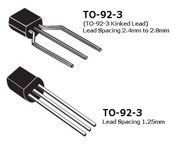

En la huella del LED TEST el cátodo queda inconfundiblemente identificado y las huellas de los 3 MOSFET se han cambiado para que la distancia entre pines sea de 2.54mm. Esto deja dos opciones para estos transistores: comprarlos con los pines más abiertos (tipo kinked leads) como los 2N7000 de Diotec (que tienen ya la separación de 2.54mm.); o darse maña con el alicate para abrirlas en los estándar (que tienen una separación de 1.25-1.27mm.).

En la huella del LED TEST el cátodo queda inconfundiblemente identificado y las huellas de los 3 MOSFET se han cambiado para que la distancia entre pines sea de 2.54mm. Esto deja dos opciones para estos transistores: comprarlos con los pines más abiertos (tipo kinked leads) como los 2N7000 de Diotec (que tienen ya la separación de 2.54mm.); o darse maña con el alicate para abrirlas en los estándar (que tienen una separación de 1.25-1.27mm.).

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Re: Va de Retro DRAM tester [Completado]

En las pruebas que estamos haciendo se ha visto que con algunas configuraciones, por ejemplo, usar un Nano con ATmega328PB o con algunos tipos de pantalla (de 0.96"), es imprescindible el par de resistencias pull-up de 10kΩ. Para solucionarlo se podrían soldar resistencias convencionales de 1/8W o 1/4W por debajo de la placa en los pines de J1 pero otra opción es, antes de soldar los pines en el adaptador SOP-8 a DIP-8, utilizar la cara de abajo para soldar dos resistencias SMD de 10kΩ entre los pines 6 y 8 y los pines 7 y 8 del PCA9536D o, lo que es lo mismo, siendo en la cara inferior entre los pines 1 y 2 y los pines 1 y 3 de la huella TSSOP-8.

En el siguiente ejemplo he utilizado dos resistencias de formato 0402 de 10kΩ aunque lo suyo hubiera sido una 0402 (entre los pines 6 y 8) y otra 0201 (entre los pines 7 y 8) pero no tenía de este valor en encapsulado 0201,

y con este minúsculo cambio será compatible con todos los tipos de Nano y pantallas.

Me disculpáis por la calidad de las ampliaciones y por las manchas, los reflejos y los brillos del flux que me resultan inevitables en las fotografías.

En el siguiente ejemplo he utilizado dos resistencias de formato 0402 de 10kΩ aunque lo suyo hubiera sido una 0402 (entre los pines 6 y 8) y otra 0201 (entre los pines 7 y 8) pero no tenía de este valor en encapsulado 0201,

y con este minúsculo cambio será compatible con todos los tipos de Nano y pantallas.

Me disculpáis por la calidad de las ampliaciones y por las manchas, los reflejos y los brillos del flux que me resultan inevitables en las fotografías.

© cacharreo

-

Gomas48K

- Aspirante a demonio

- Mensajes: 277

- Registrado: 16 Jun 2021, 06:08

- Ubicación: España

- Has thanked: 726 times

- Been thanked: 221 times

Re: Va de Retro DRAM tester [Completado]

Parece microcirugía!

Solventando todo lo que se interpone en el camino.

Solventando todo lo que se interpone en el camino.

Con mi Gomas 48K, hasta el mismo infierno!!!

-

cacharreo

- Moderador

- Mensajes: 6121

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1249 times

- Been thanked: 3004 times

- Contactar:

Re: Va de Retro DRAM tester [Completado]

Te lo agradezco pero, para que conste, el experimento no estuvo a salvo de problemas más que esotéricos.

Tan pronto lo completé y antes de soldar los pines para enchufarlo al tester lo comprobé con el polímetro, y mientras que entre los pines 6 y 8 medía una resistencia de alrededor de 10kΩ, entre los pines 7 y 8 tenía una resistencia de unos 18.5Ω. A sabiendas de que la resistencia entre los pines 7 y 8 del integrado es cuasi-infinita, comprobé y recomprobé en la hipótesis de que durante la soldadura la resistencia había hecho un microcontacto no deseado, por ejemplo, por debajo de su cuerpo. Pero no hubo forma de encontrar ningún problema parecido así que desoldé esa resistencia y fuera del conjunto la medición era no casualmente de 18.5Ω. En definitiva, mi tira de resistencias 0402 (y por tanto sin serigrafía) de 10kΩ±1% teóricamente de Yageo pero comprada en AliExpress, incluía misteriosamente en su segunda posición una resistencia de 18Ω. Una vez sustituida por la siguiente de la tira, que si era de 10kΩ porque lo comprobé antes, el invento funcionó. Son cosas inexplicables. Ah, para los escépticos, no tenía ningunas otras resistencias de ningún tipo en la mesa de trabajo que pudieran haber contaminado la muestra.

© cacharreo