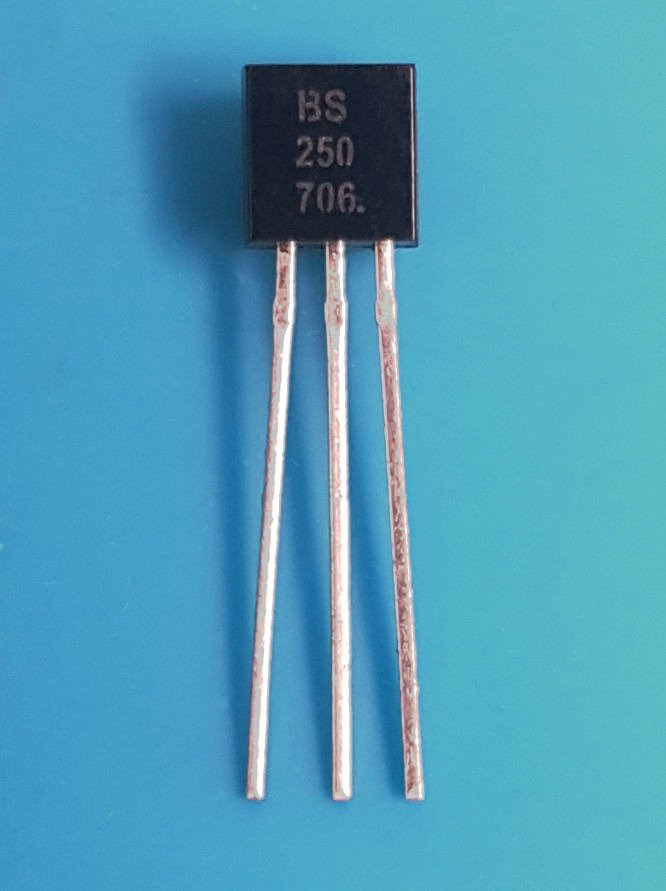

Sentimos informaros que lamentablemente hemos encontrado falsos transistores MOSFET entre los distribuidos en los kits. Por favor, leed este texto cuanto antes para confirmar si disponéis de los BS250 genuinos o no antes de soldarlos. Gracias.

Los testers que se solicitaron montados no están afectados porque salen completamente probados.

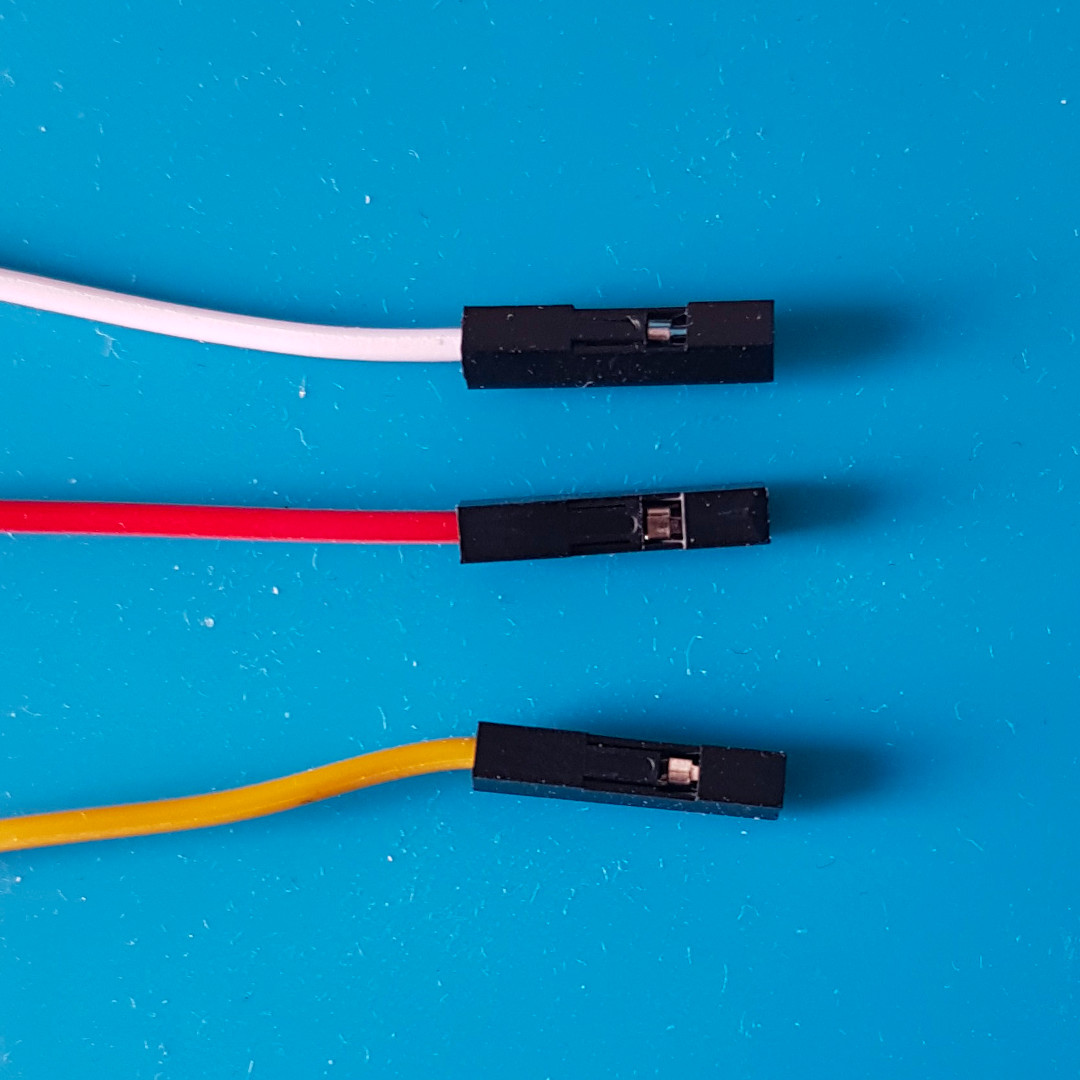

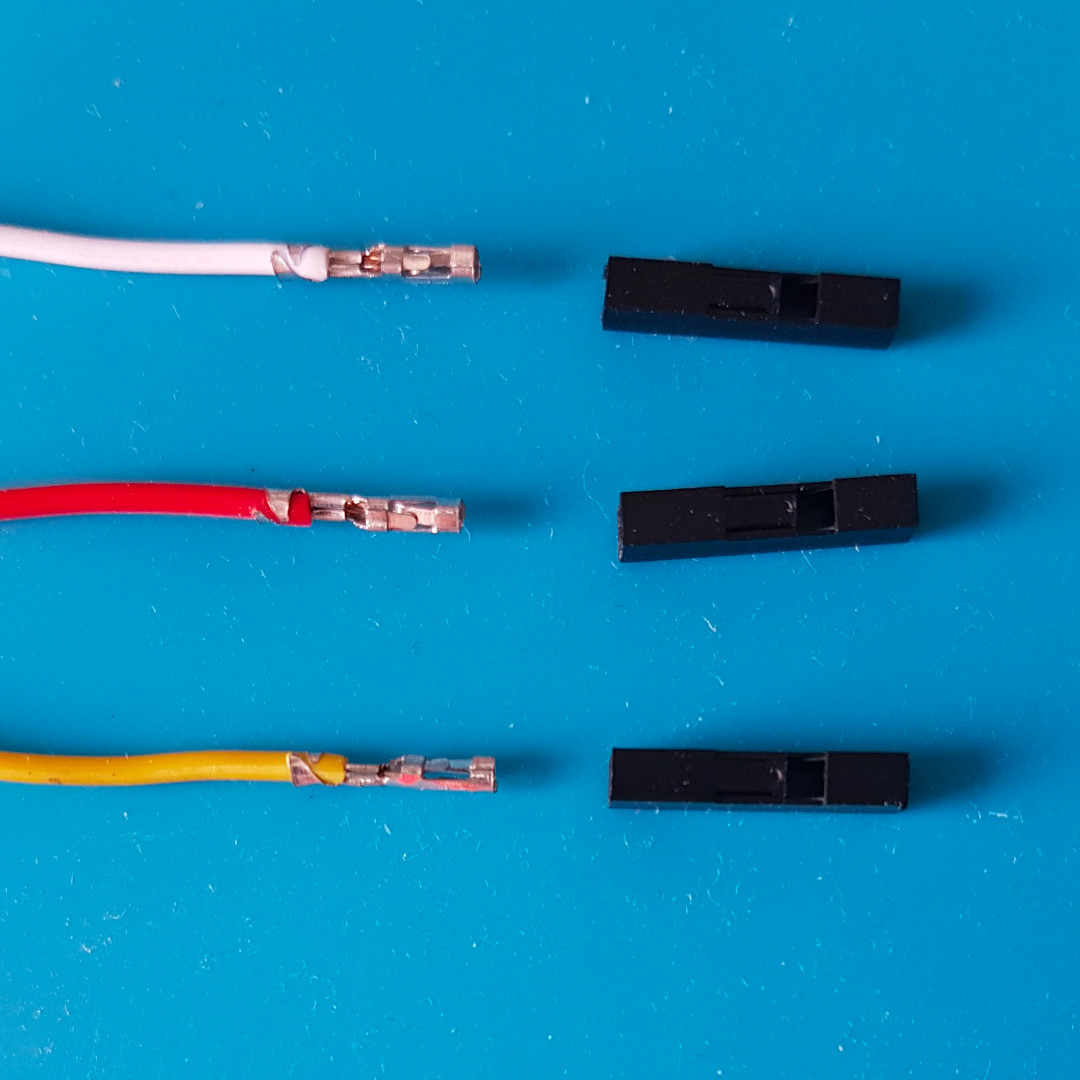

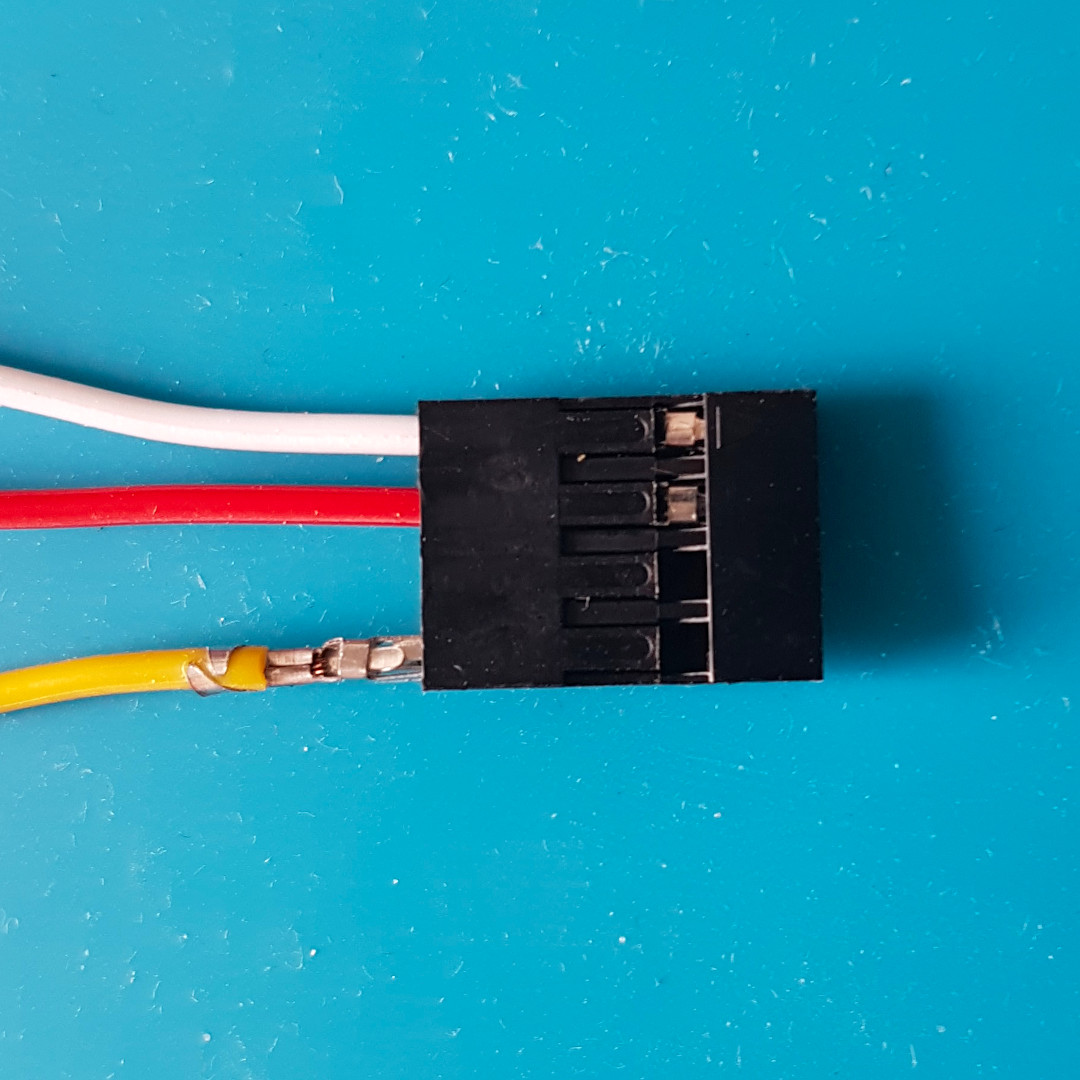

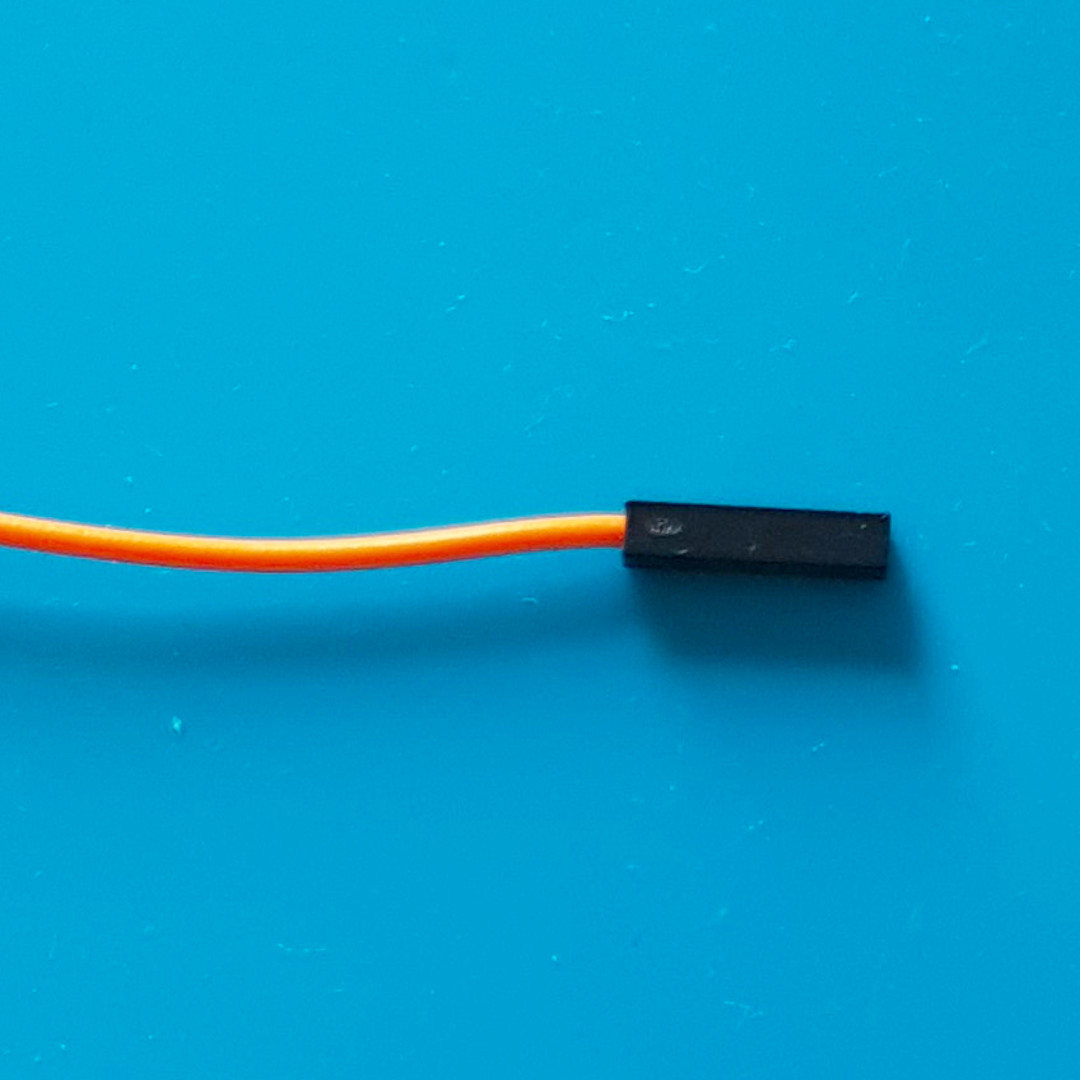

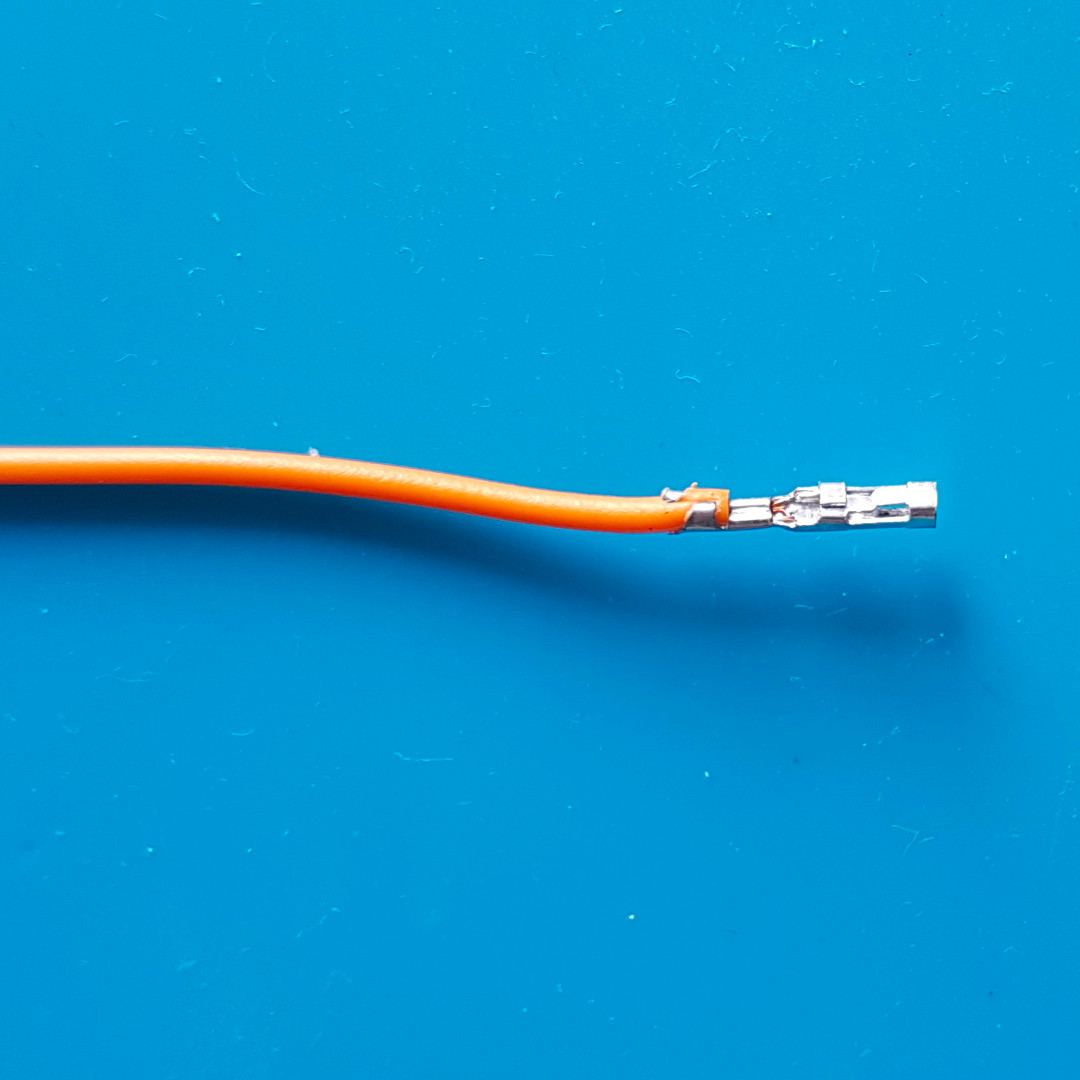

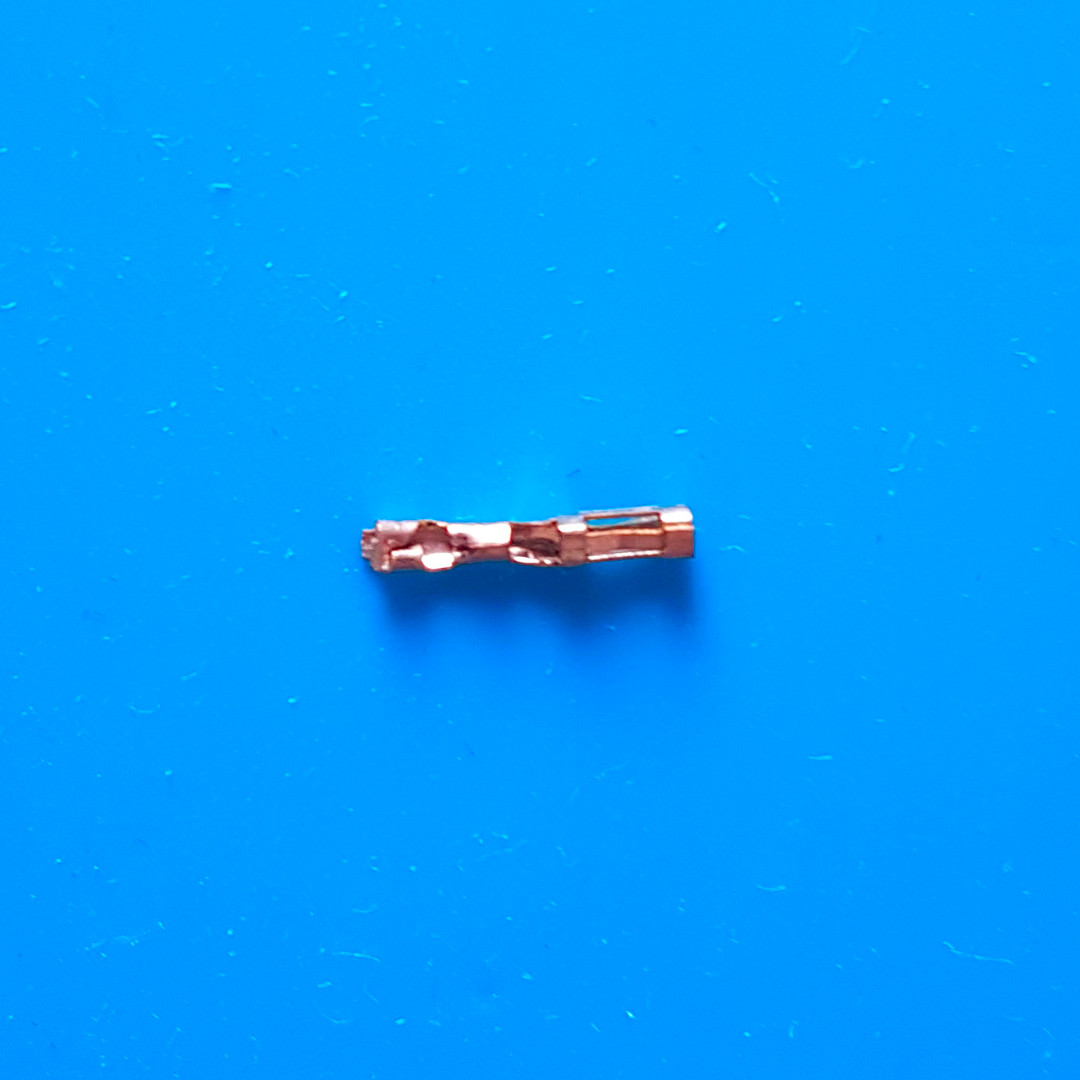

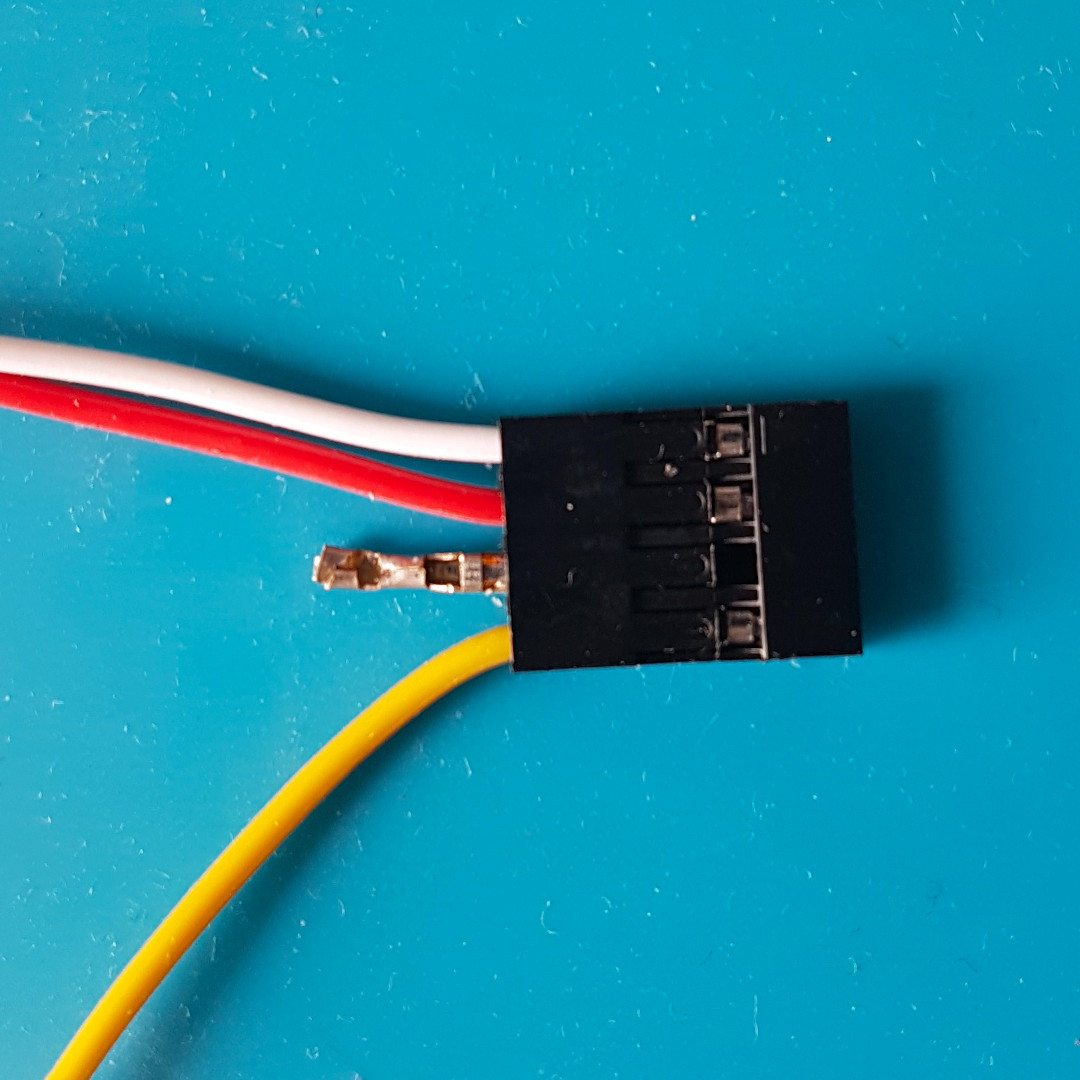

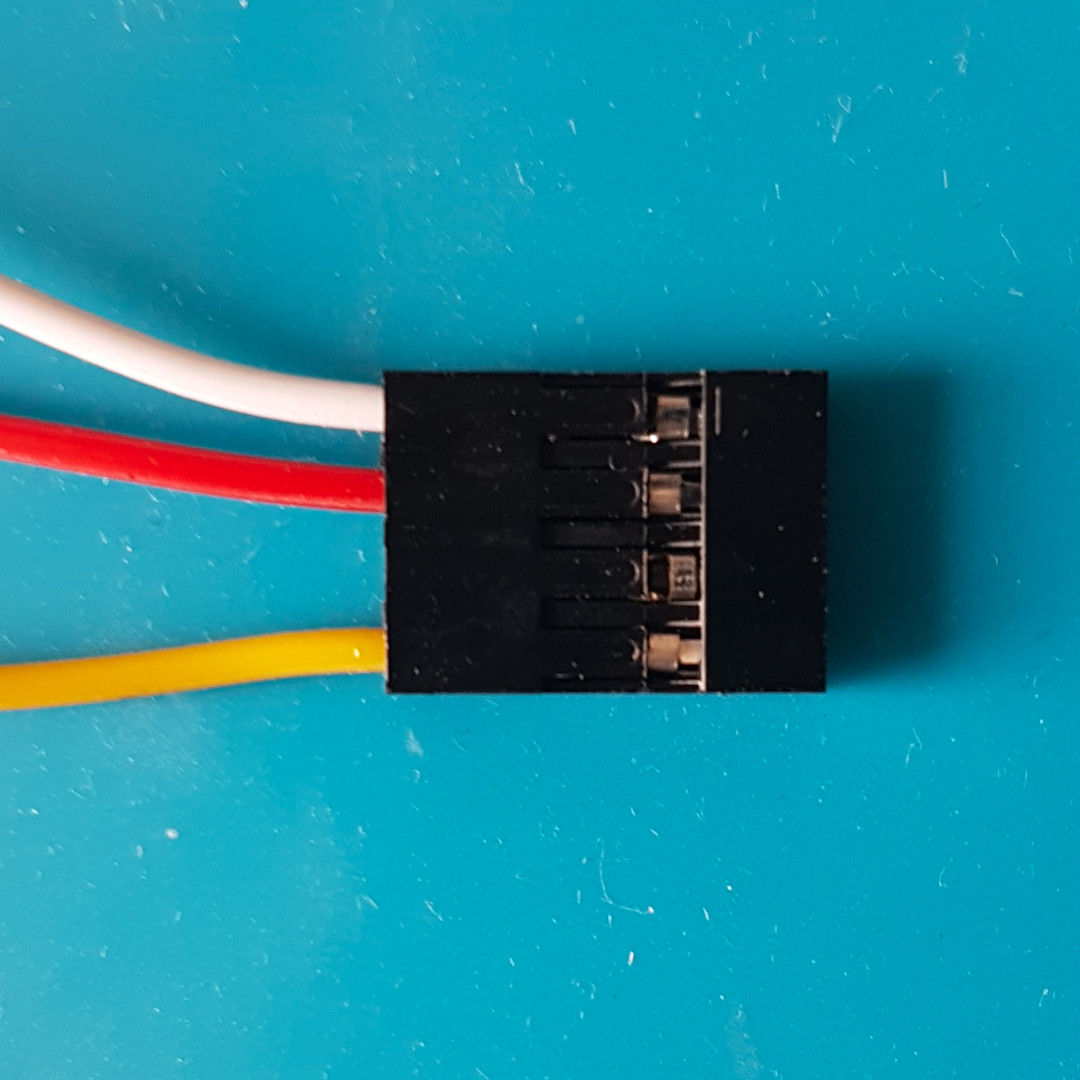

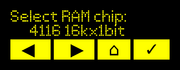

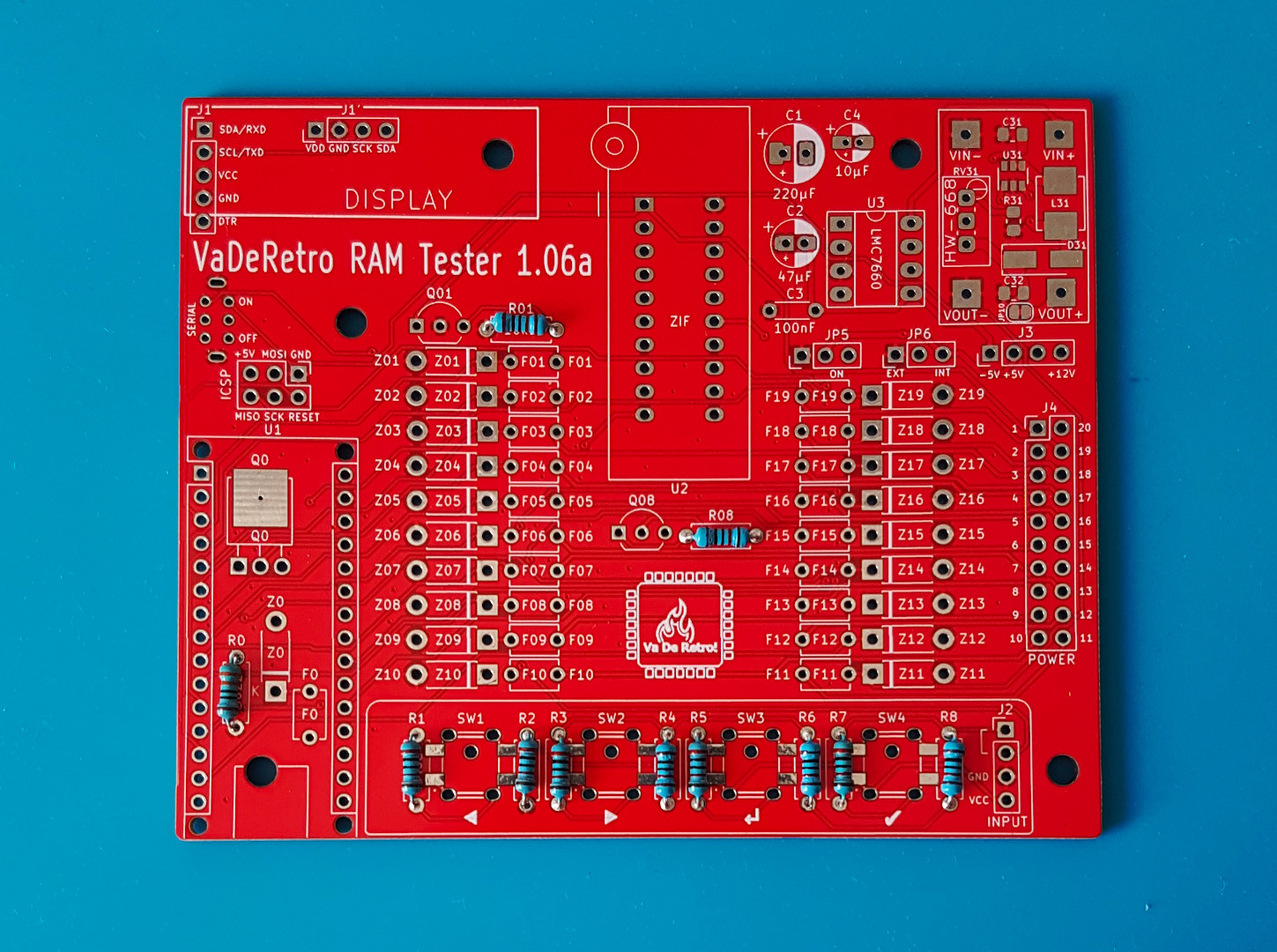

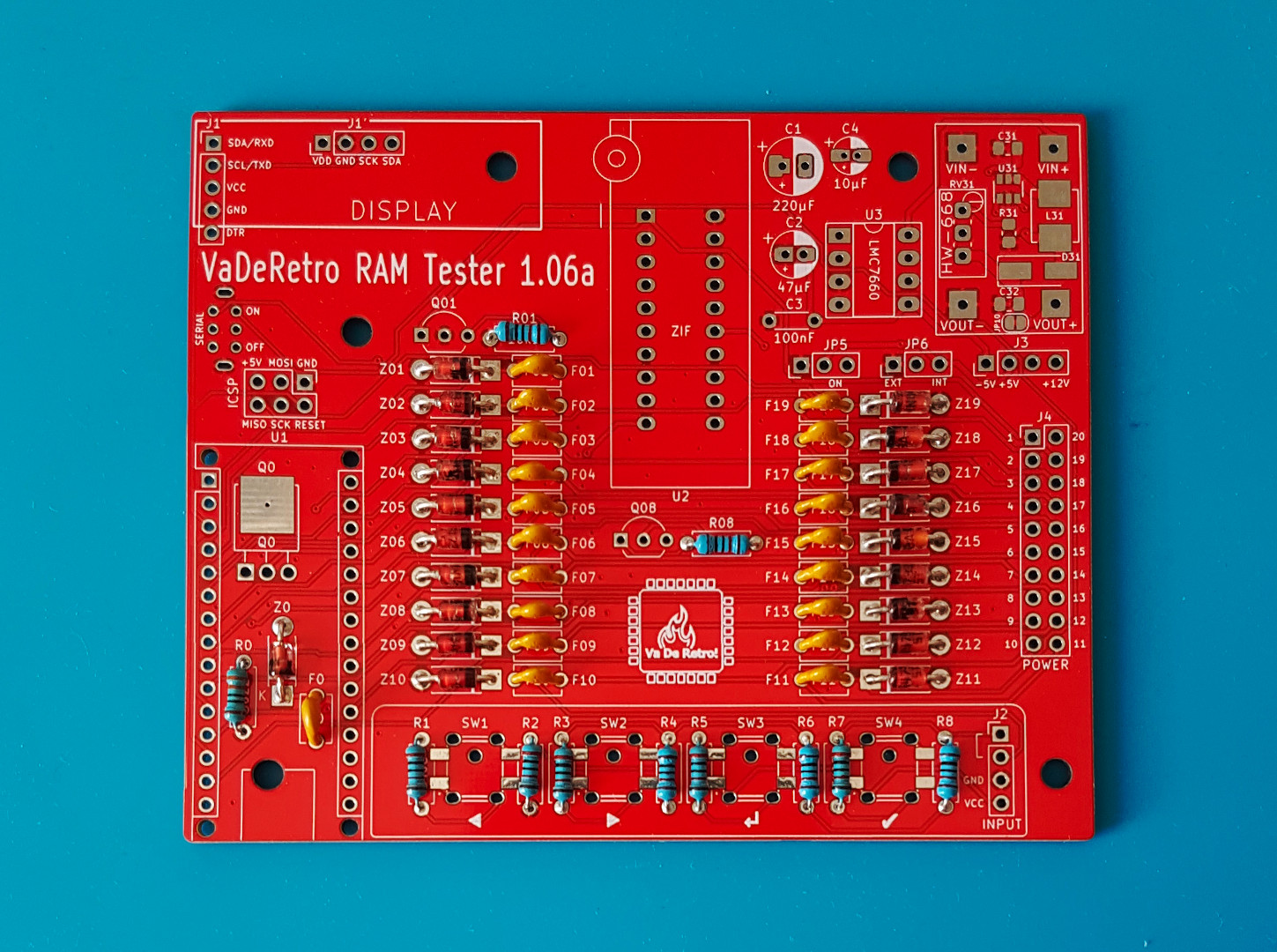

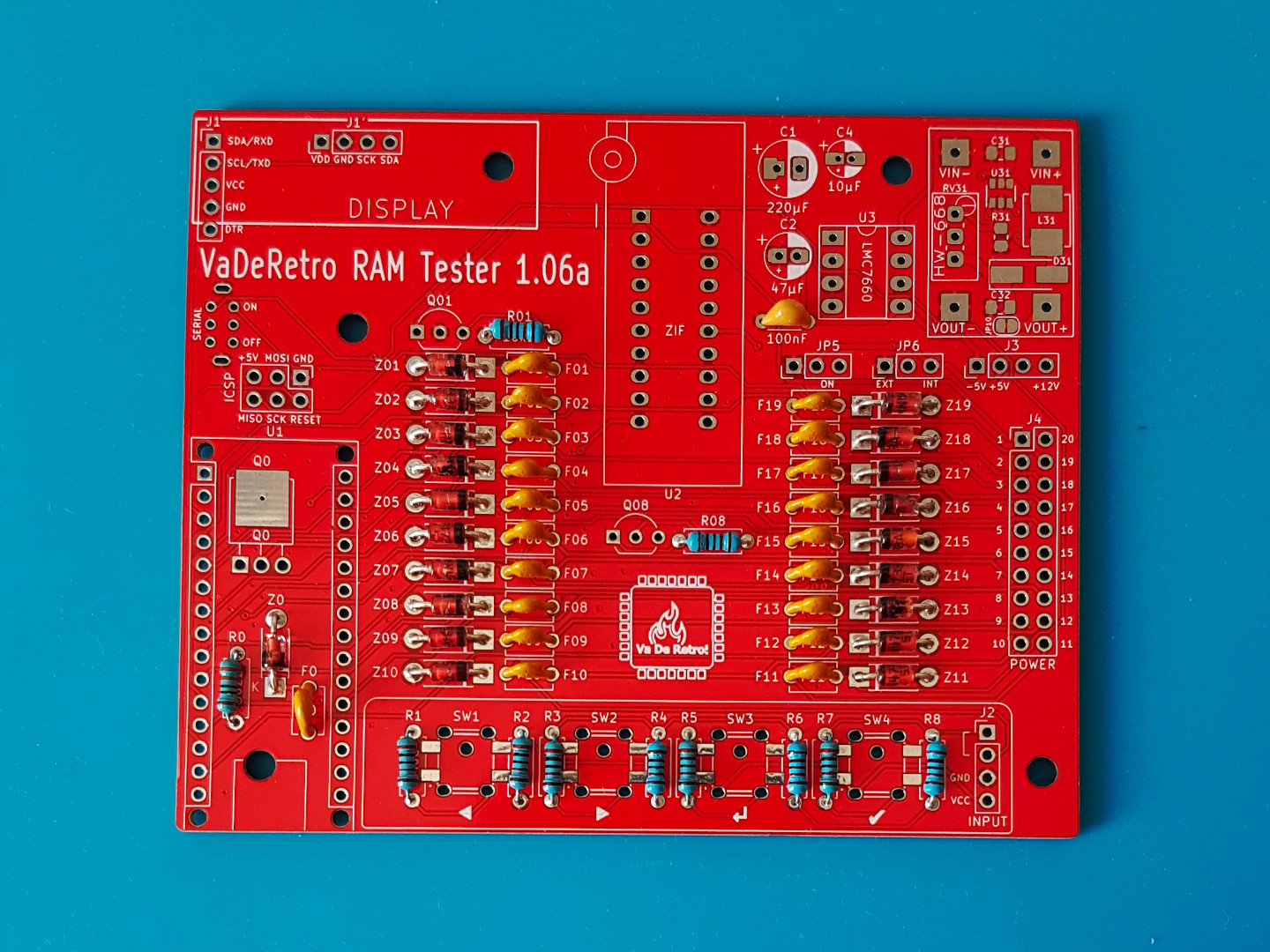

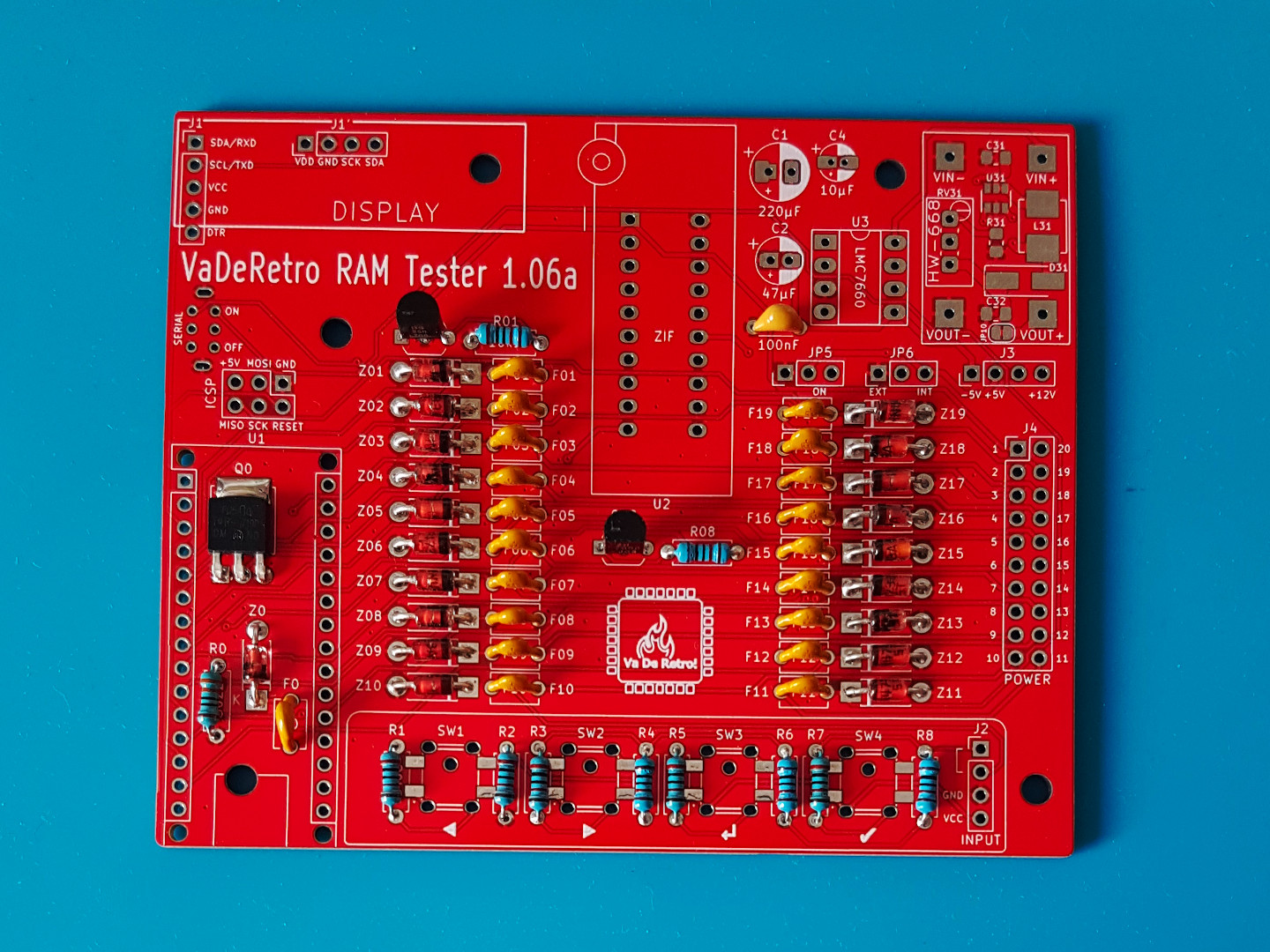

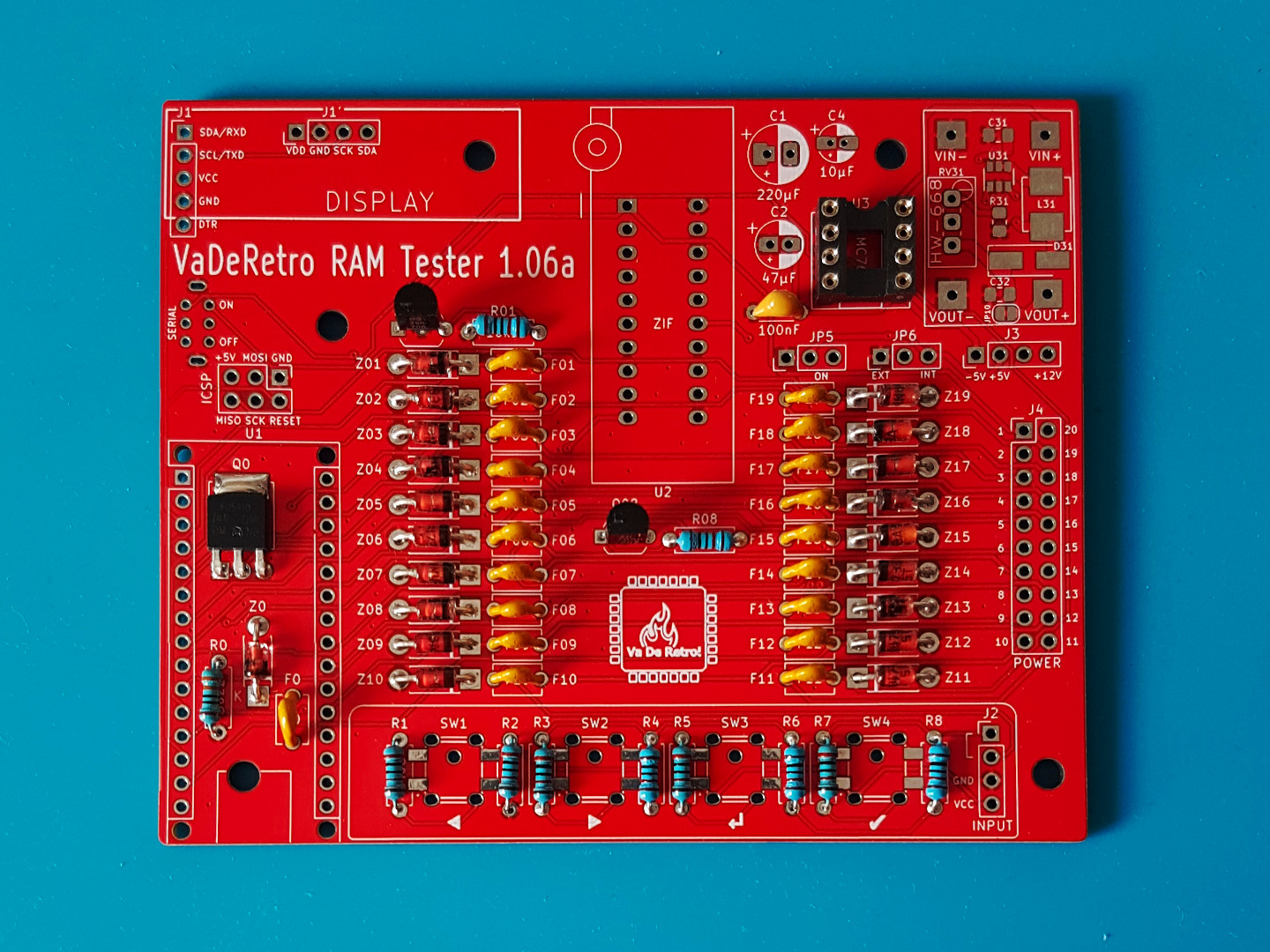

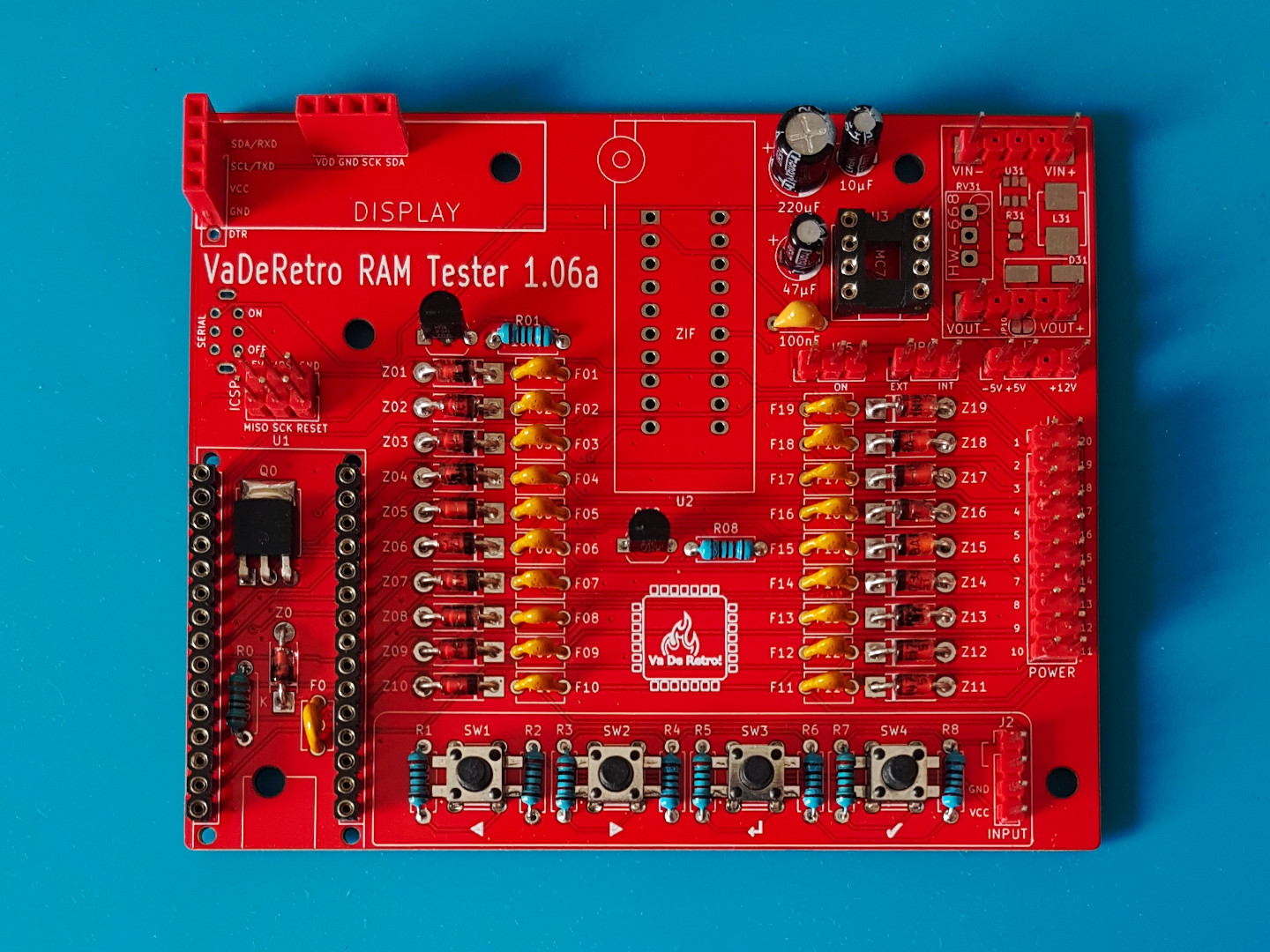

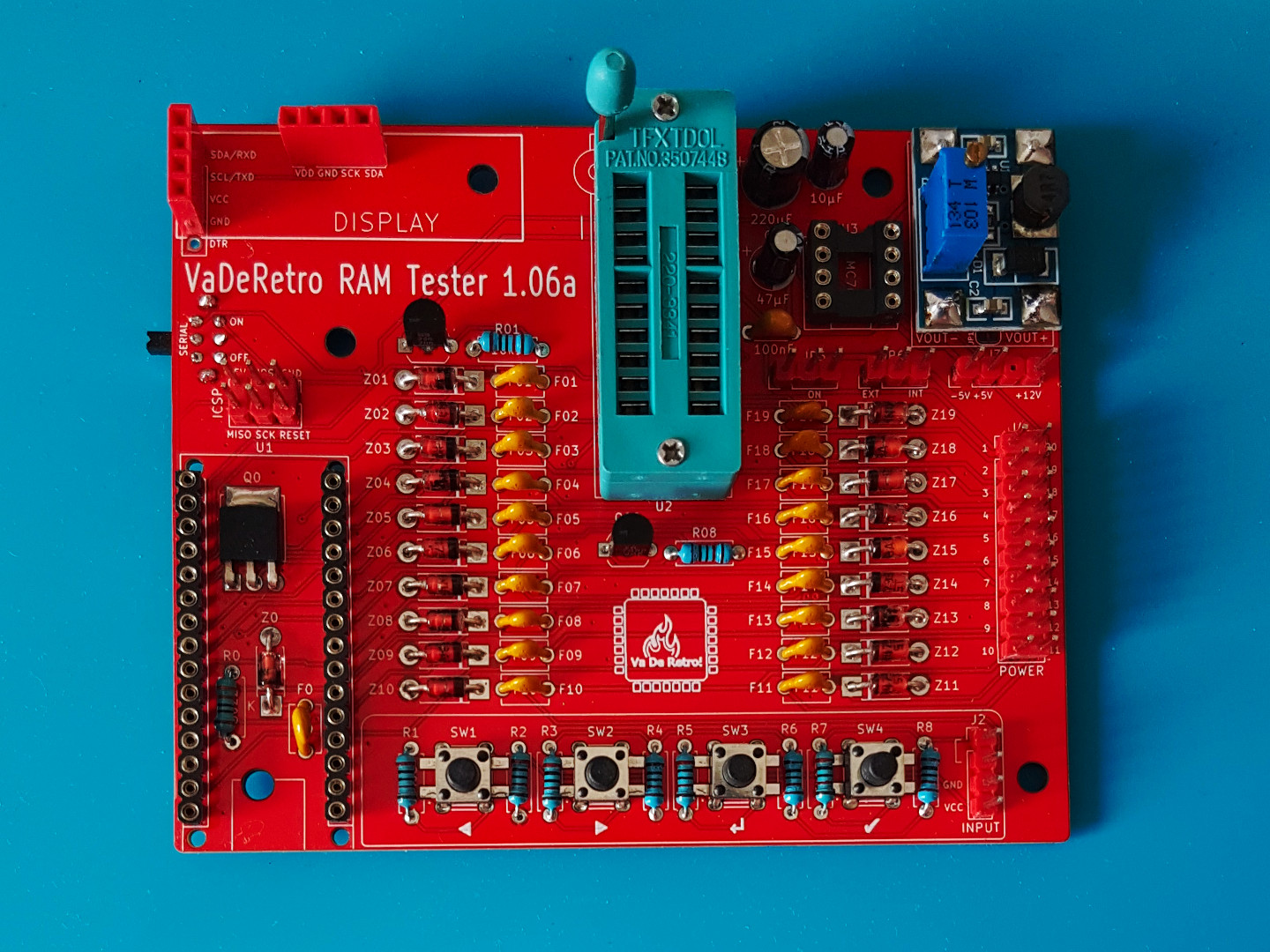

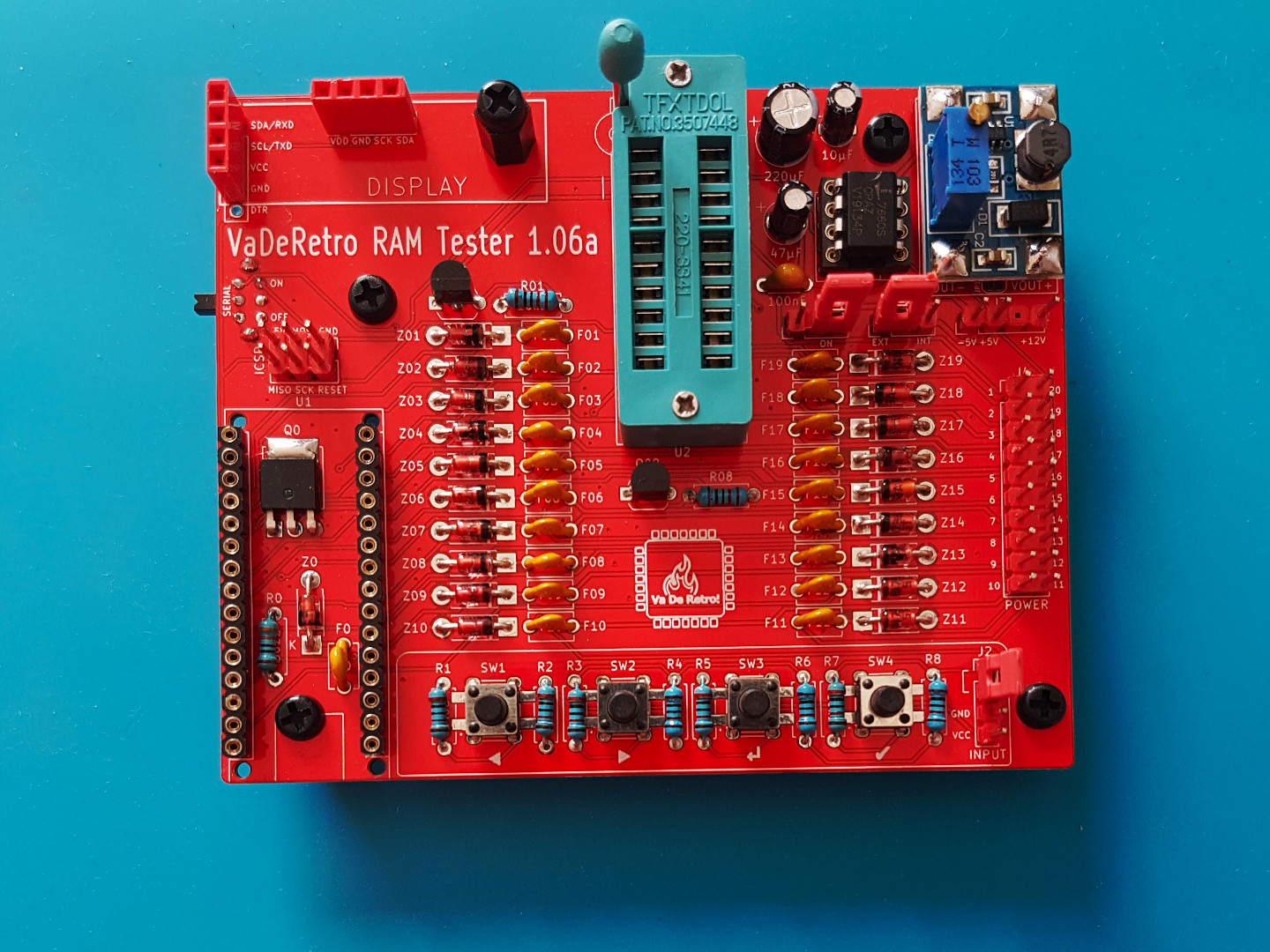

Saltar directamente a... • Guía de montaje para el juego de cables J3' • Guía rápida de ajuste del tester • Ejemplos de uso • Guía rápida de resolución de problemas • Tabla de búsqueda de tests • Guía de referencia rápida (manual) • Desempaque y puesta en marcha de los testers montados • Reacciones a estas guíasEste es un tutorial para el montaje de la v1.06x del VdR DRAM tester siguiendo la lista de componentes (BOM) recomendada.

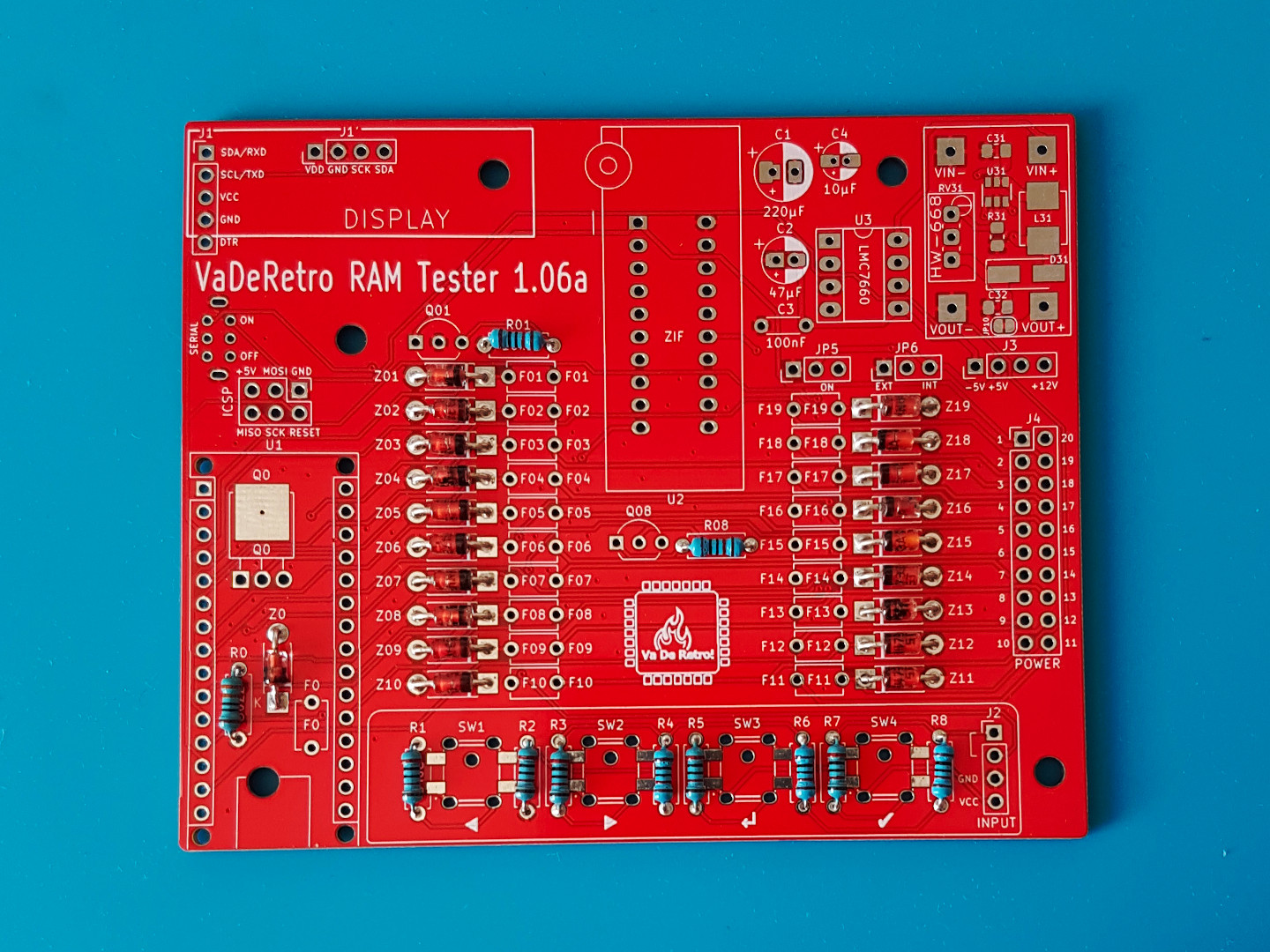

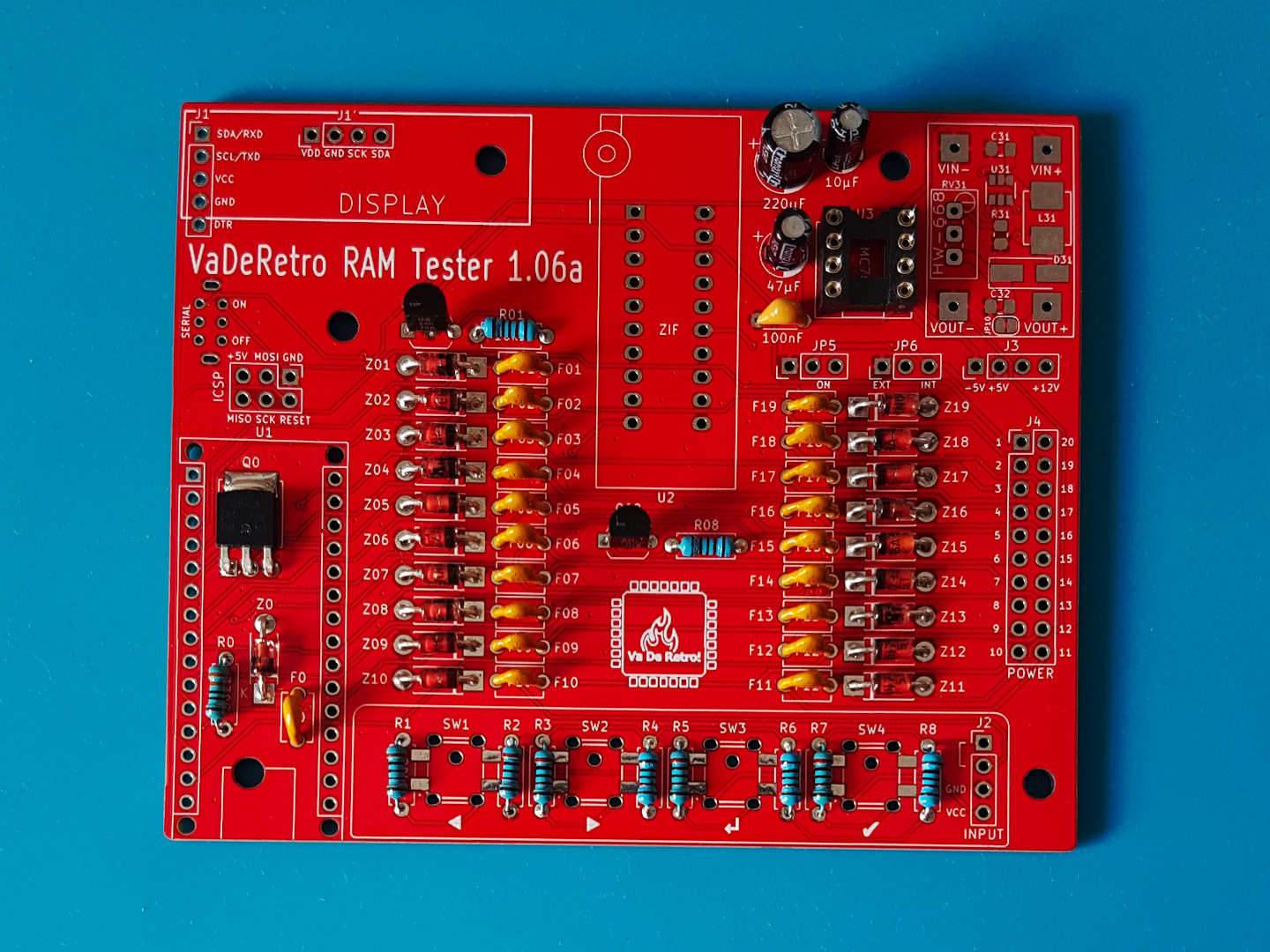

1) Una vez limpiada la placa con alcohol isopropílico, comenzamos soldando las resistencias R0, R4, R6, R8, R01, R08, R1, R2, R3, R5 y R7.

2) Continuamos soldando los diodos zener (Z0 y Z01-Z19) teniendo especial atención a su orientación/polaridad.

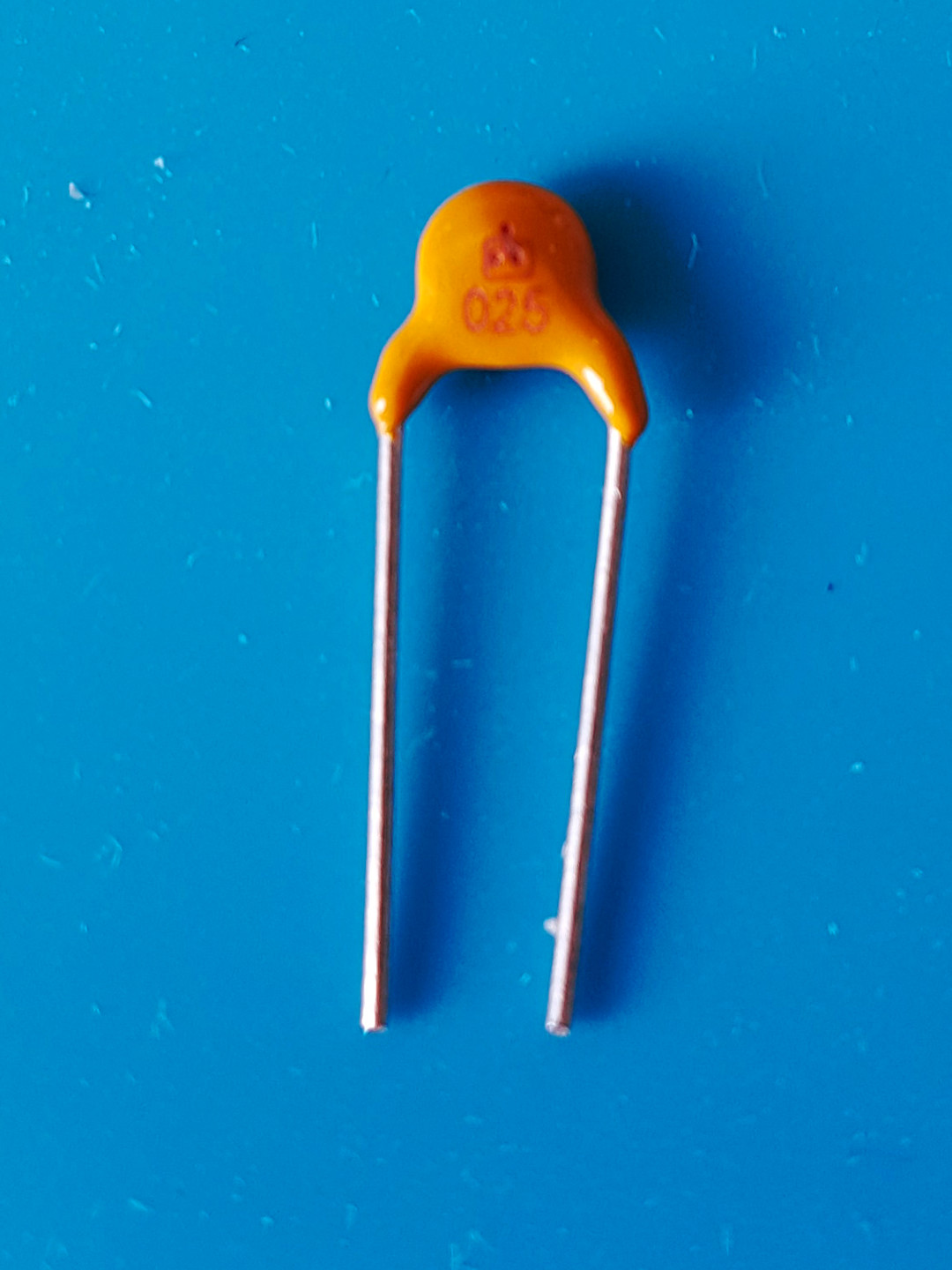

3) Soldamos el fusible F0 de 6V 250mA pero no sin antes comprobar su serigrafía (025) para evitar confusiones (con los fusibles de 30mA o con el condensador cerámico de 100nF).

4) Comprobamos la serigrafía (003) de los fusibles de 30mA (F01-F19) para evitar confundirlos con el condensador cerámico de 100nF, y los soldamos.

5) La serigrafía del condensador cerámico de 100nF (C3) muestra la inscripción 104, una vez comprobada lo soldamos.

6) Soldamos el transistor MOSFET (Q0) IRFU5410.

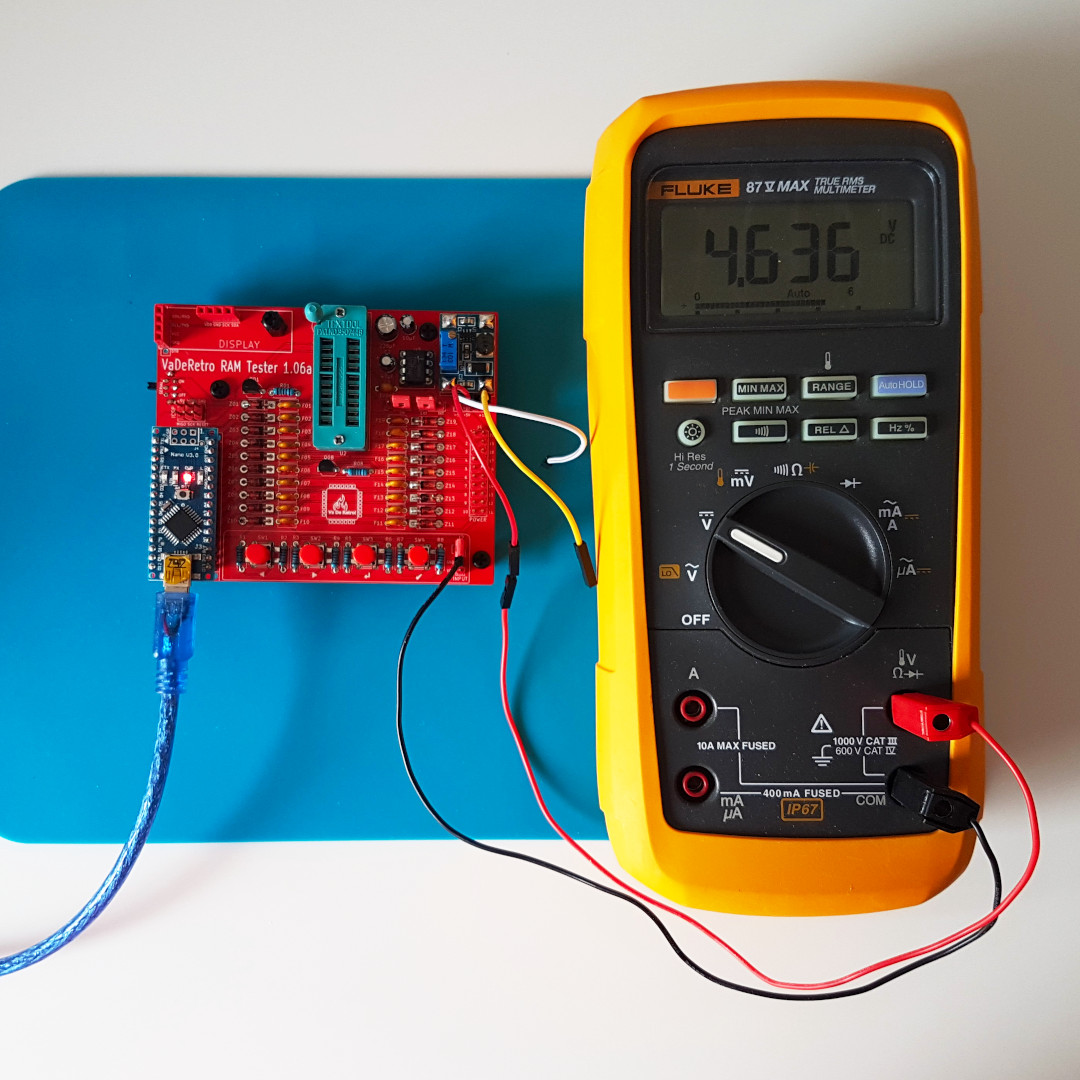

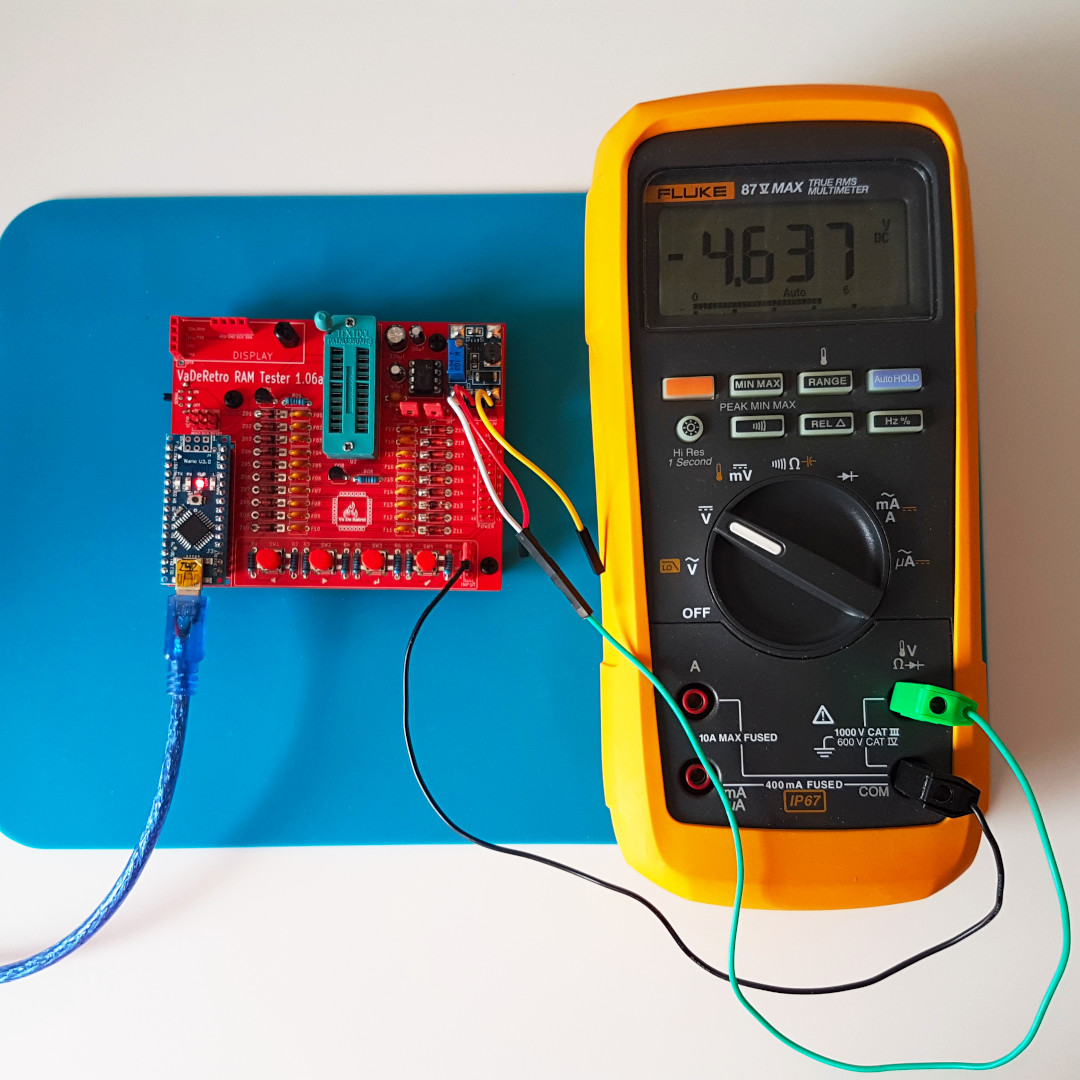

7) Antes de continuar vamos a comprobar si el transistor MOSFET Q01 con referencia BS250 es genuino o remarcado para así evitar tener que desoldarlo y sustituirlo.

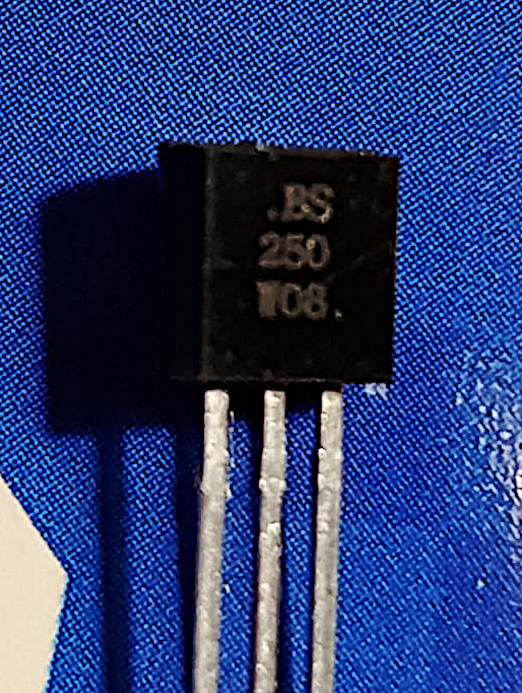

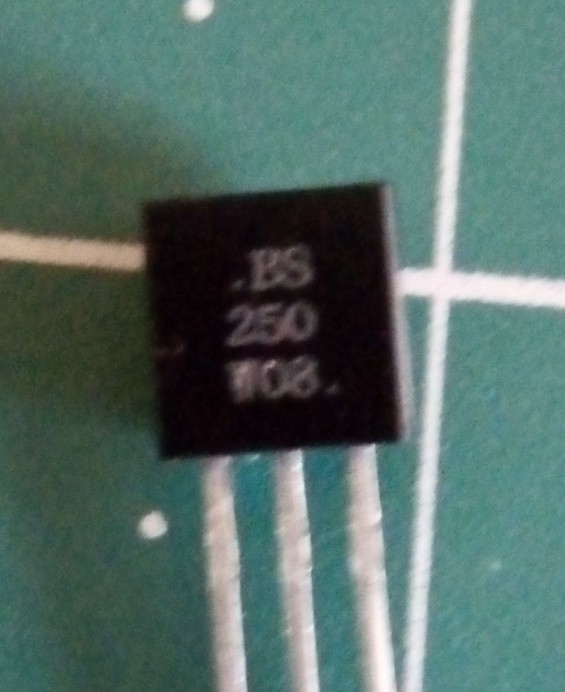

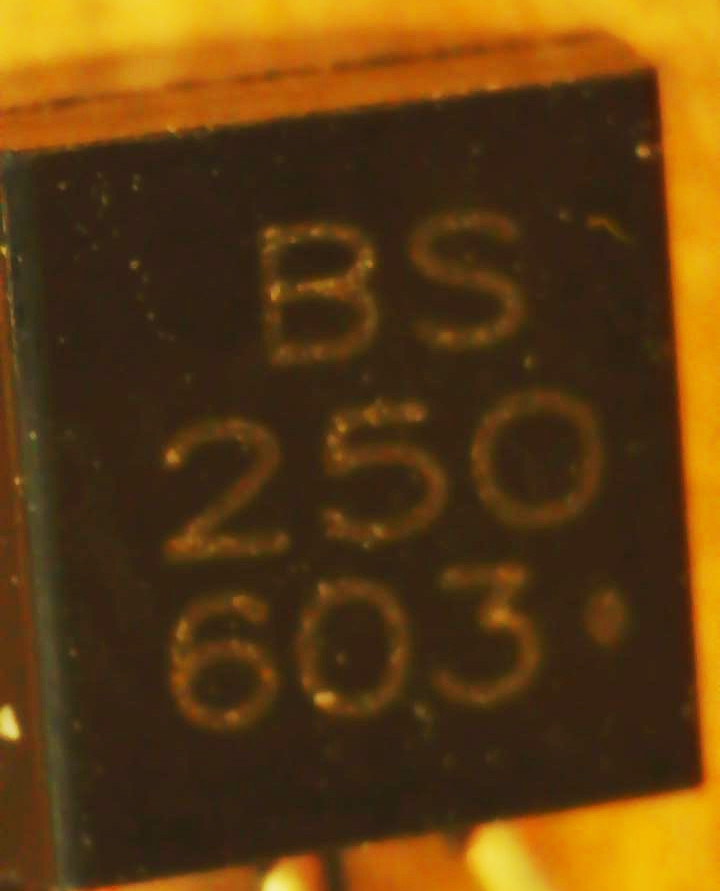

Un BS250 genuino presenta esta serigrafía,

o esta otra:

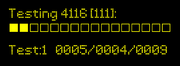

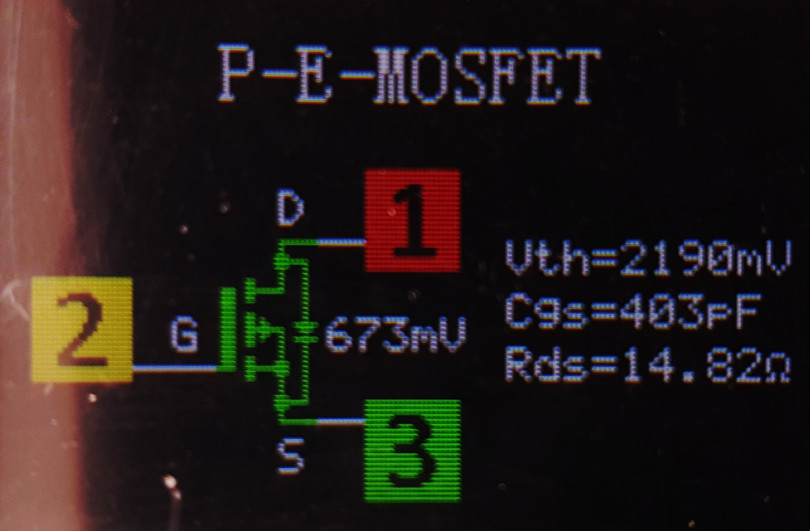

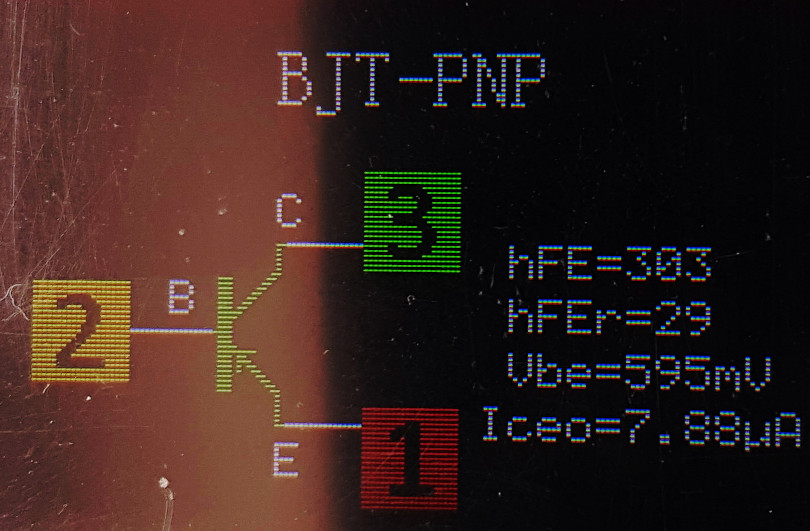

y utilizando un comprobador de transistores (TC1, LC1, T4, T7, MTT-V1,...) ofrecerá esta información:

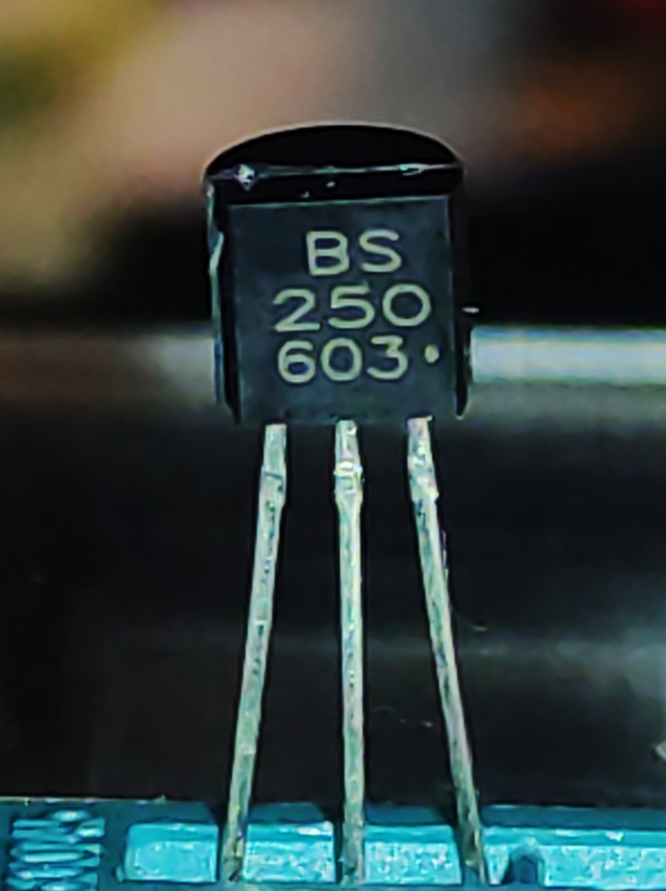

Por contra un BS250 remarcado (que posiblemente sea en realidad un transistor PNP BJT S9015) tiene esta serigrafía,

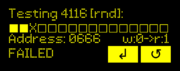

y puesto en el comprobador de transistores mostrará esta información:

Importante: Si en alguno de los kits encontráis uno de estos BS250 remarcados, por favor enviadnos un mensaje privado a @Rebobinando o a @cacharreo a la mayor brevedad. Para cualquier duda también podéis contestar en este tema o contactarme por mensaje privado, como prefiráis.

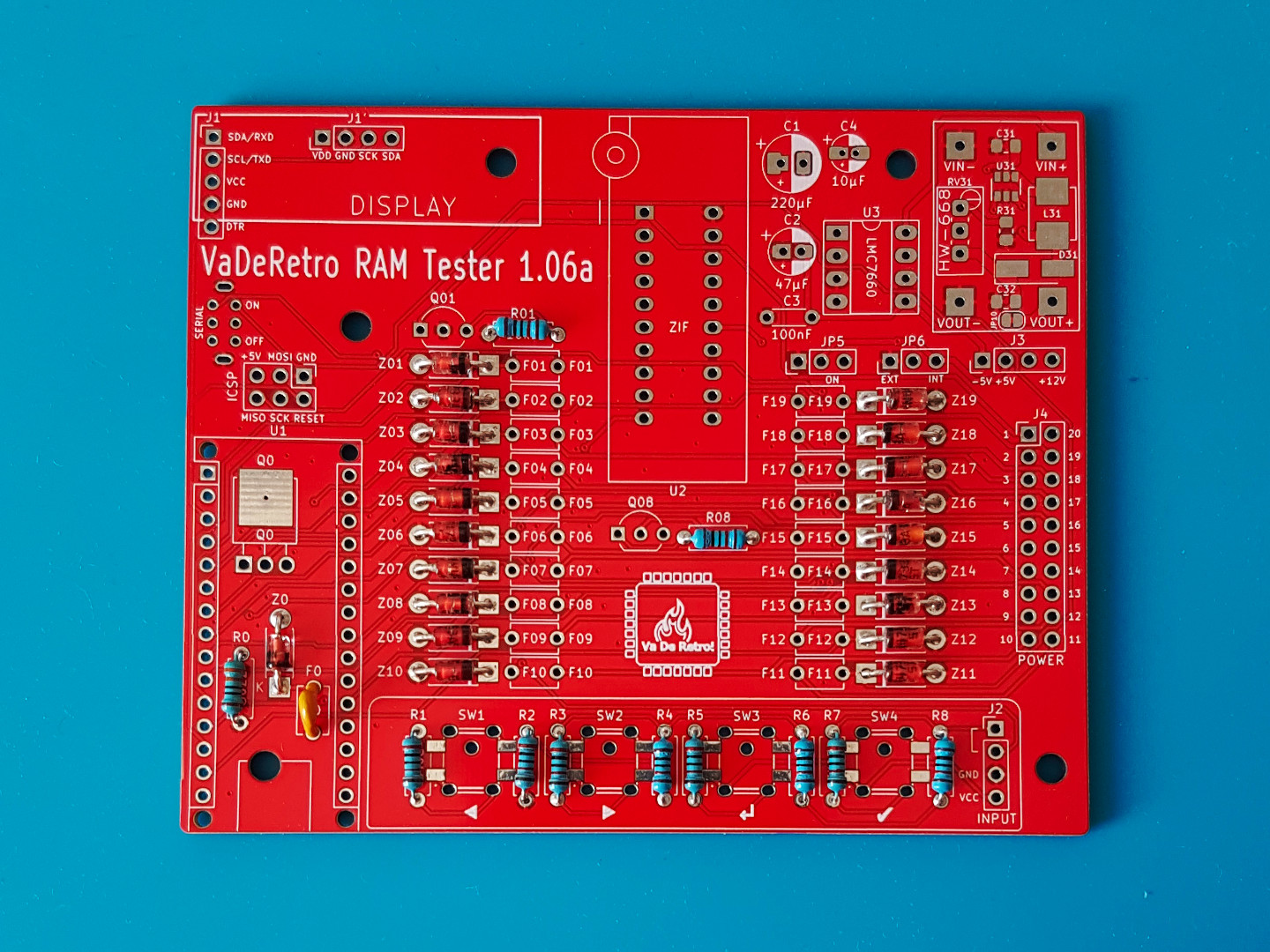

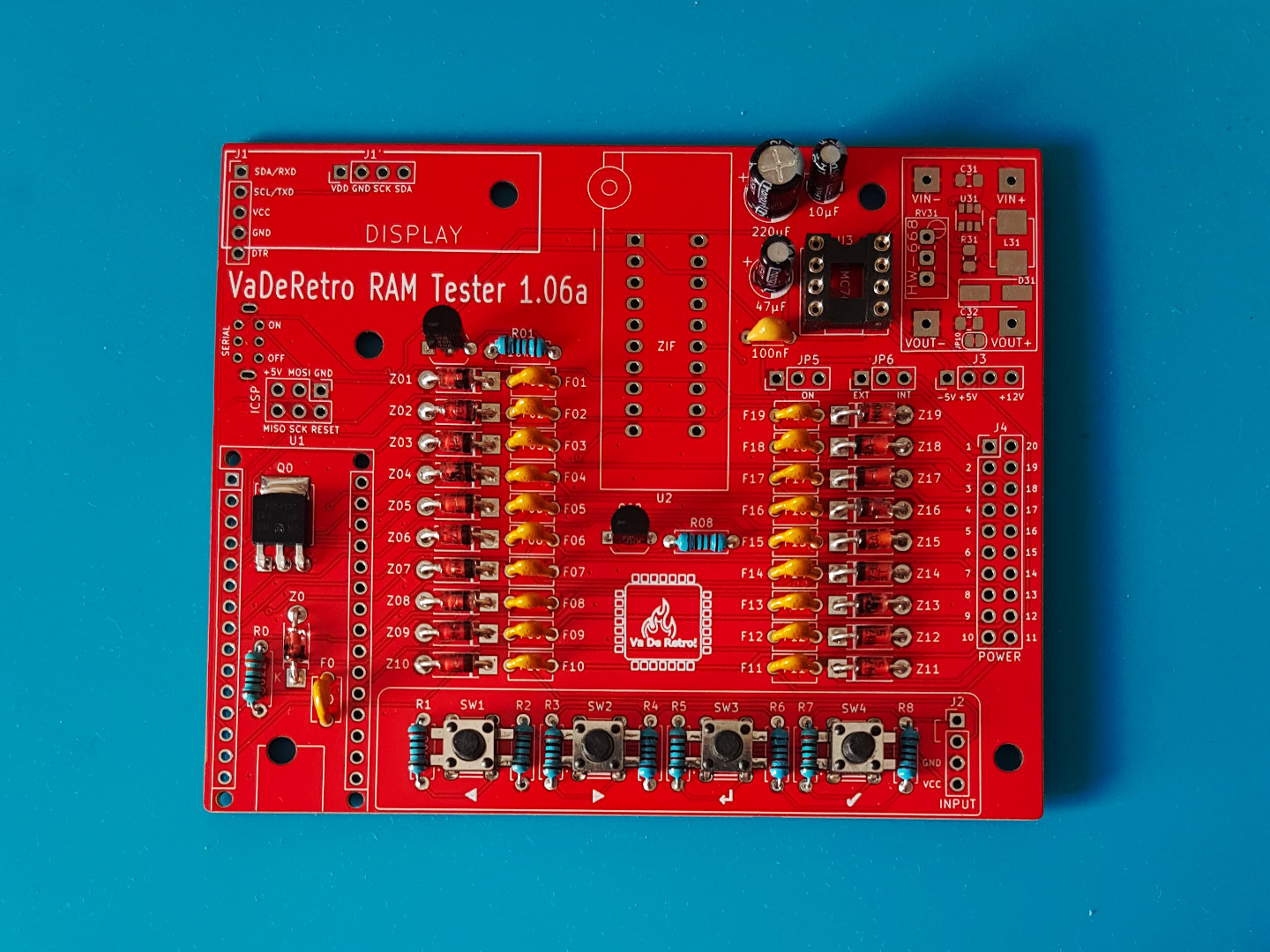

Una vez comprobado que el BS250 (Q01) es genuino lo soldamos en la parte superior de la placa (a la izquierda de R01) y después el 2N7000 (Q08) situado en la parte central de la placa (a la izquierda de R08). Es recomendable comprobar dos veces la serigrafía de ambos transistores antes de soldarlos porque más de una vez ha ocurrido que se han cambiado uno por otro.

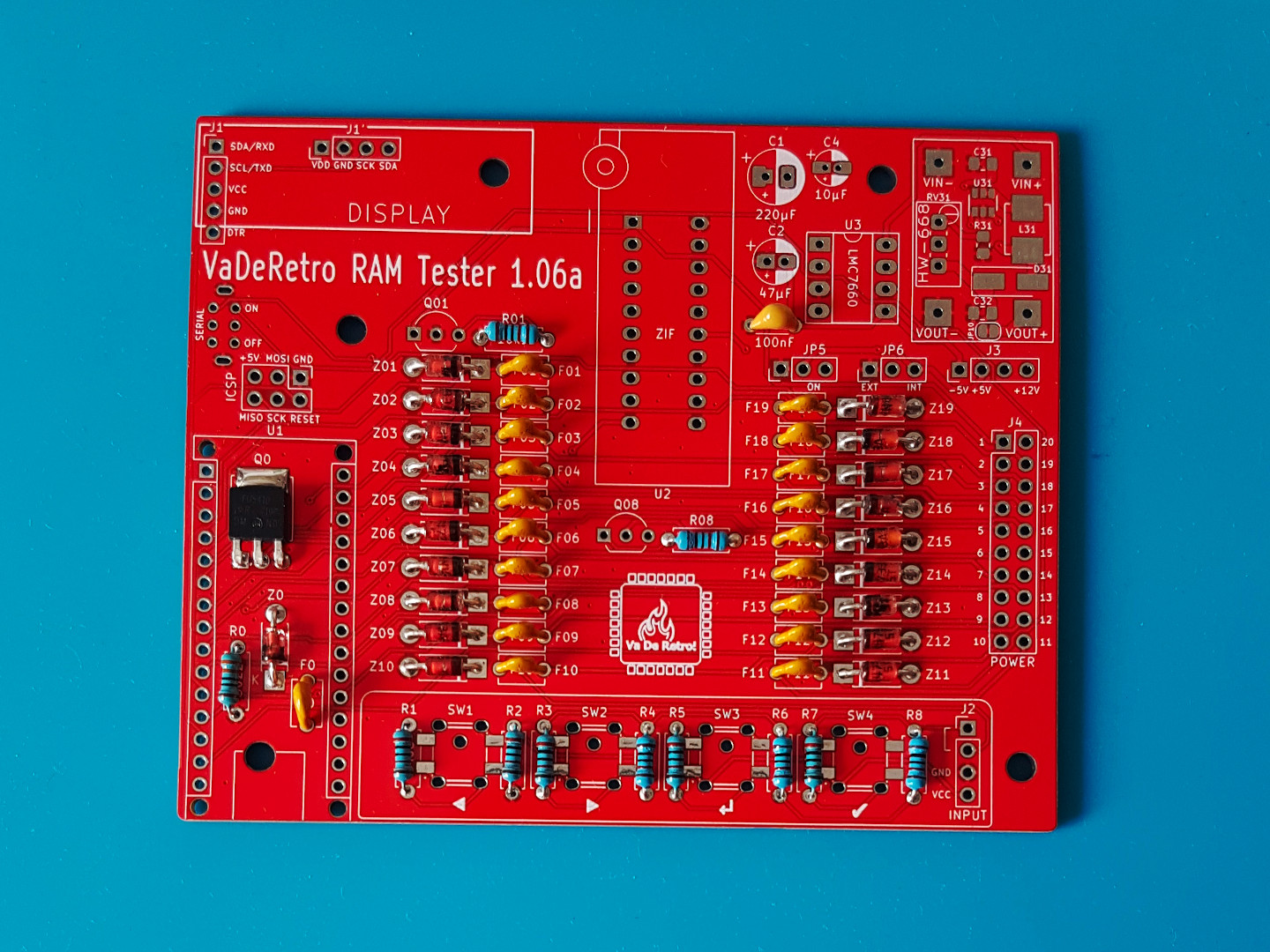

según el número de revisión de la placa estos transistores pueden tener una de estas dos formas:

para el formato de la izquierda en la imagen (inline), se recomienda utilizar un soldador de punta fina, estaño de 0.3mm a 0.5mm y/o flux. Si no es posible, con flux es suficiente para lidiar con estas distancias entre los pads.

8) Continuamos soldando el zócalo DIP-8 (para U3).

9) Soldamos los tres condensadores electrolíticos, C4, C2 y C1, respetando la polaridad indicada tanto en el cuerpo de cada condensador como en la placa.

10) Seguimos con la soldadura de los pulsadores SW1-SW4. Antes de soldar hay que asegurarse que las patas de plástico que están bajo cada pulsador están en perfecto contacto con la placa, para evitar que queden soldados inclinados.

11) Preparamos la tira de pines 1x04 para J3 extrayendo (p.e. con unos alicates) el tercero de los pines y soldamos las tiras de pines para J1, J1', J2, J3, JP6 y J4.

Independientemente de la versión de la placa, después se suelda la tira de pines 1x02 macho JP5 de forma que su pin más a la derecha coincida con el agujero para el pin más a la derecha en la placa. Dicho de otro modo, en caso de que nos sobre un agujero en la placa, éste quedará a la izquierda, es decir, en la placa solo consideramos los dos agujeros de JP5 más a la derecha.

Pasamos a soldar J1 teniendo en cuenta que debe quedar alineado lo más arriba posible porque el último pin, serigrafiado con DTR, no lo utilizaremos.

12) Se sueldan las dos tiras de agujeros redondos 1x15 (J5) que servirán de zócalo para el Nano.

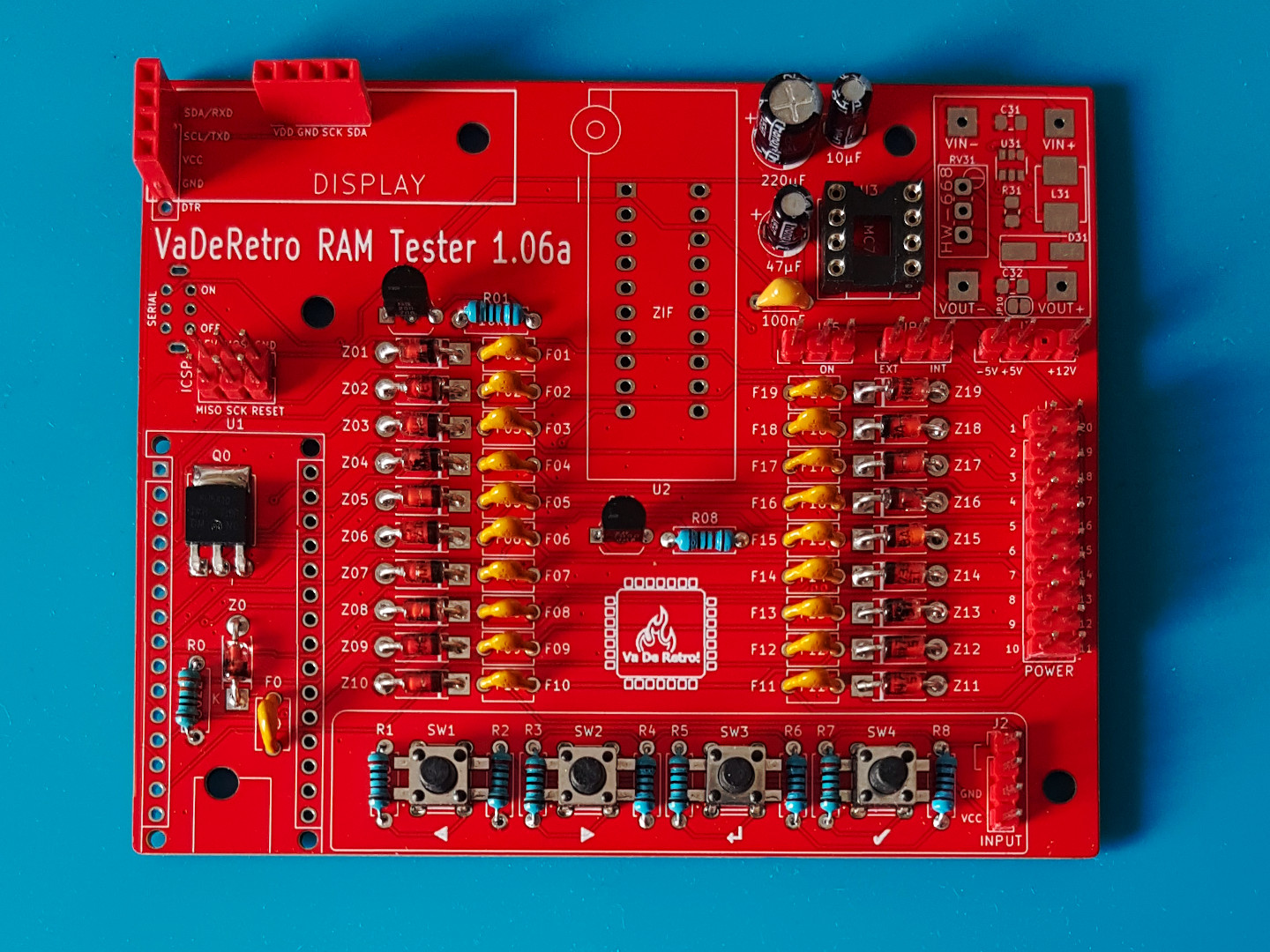

Preparamos las tiras de pines 1x05 que servirán de soporte al módulo HW-668, extrayendo uno a uno todos los pines excepto el primero y el último. Una vez listas, las soldamos como se ve en la siguiente foto.

13) Soldamos el conmutador SW0, el único componente cuyas soldaduras quedan en la parte superior de la placa.

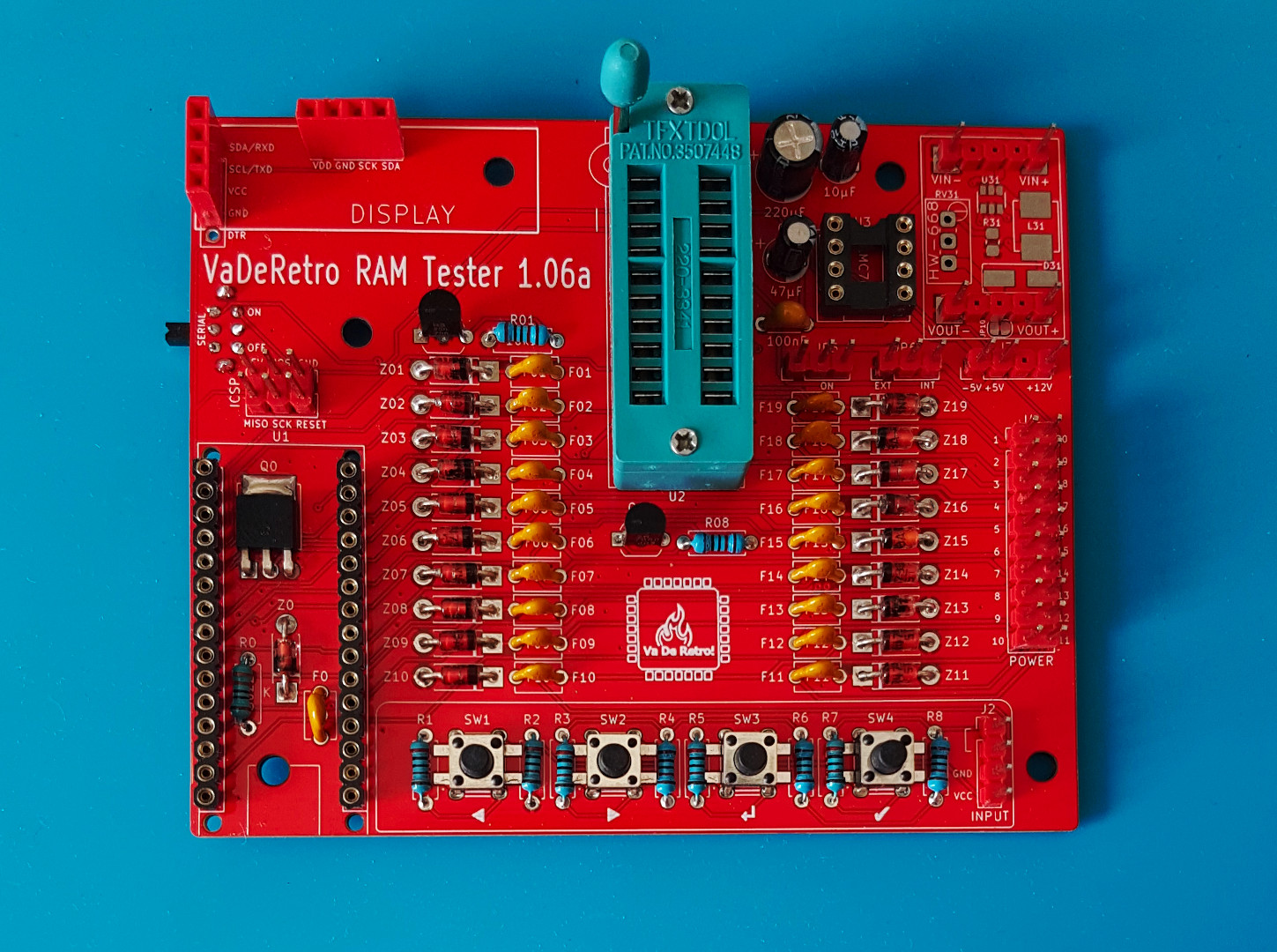

14) Se suelda el zócalo ZIF de 20 pines (U2).

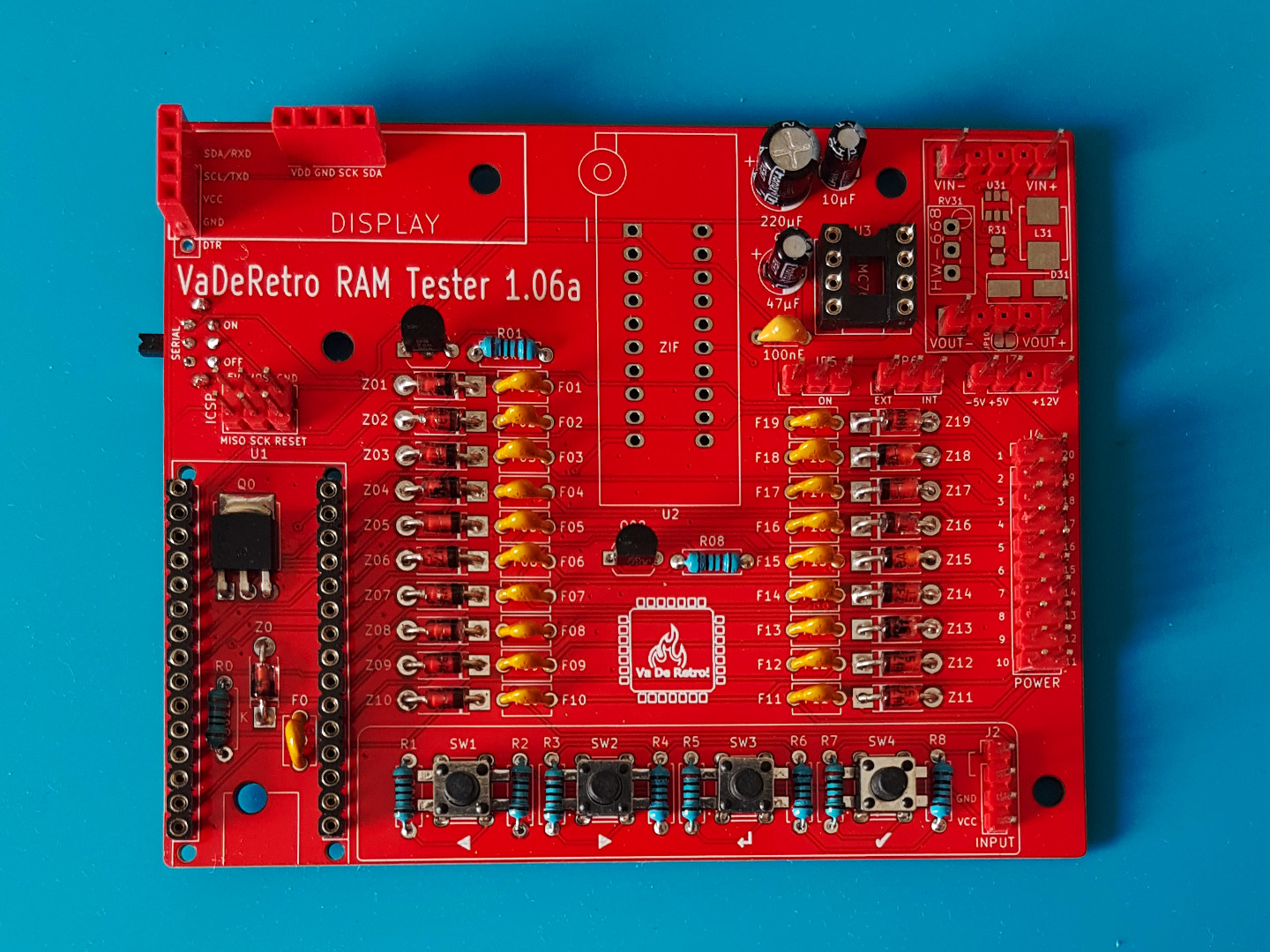

15) Instalamos el conversor DC-DC (HW-668) en la placa, soldándolo a los 4 pines preparados al efecto y cortando el exceso. La orientación es la que se muestra en la fotografía, con el potenciómetro azul hacia la zona interior de la placa.

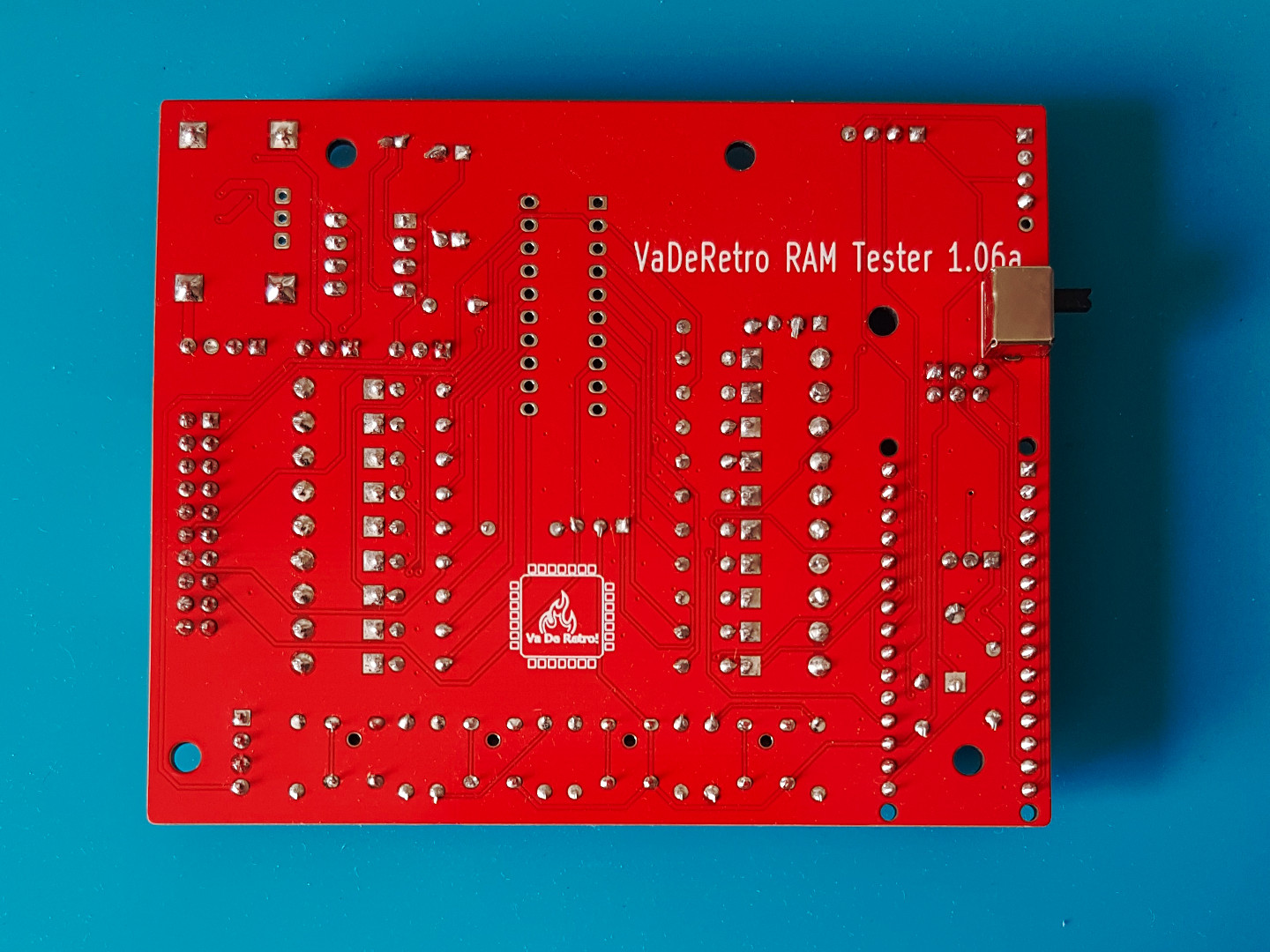

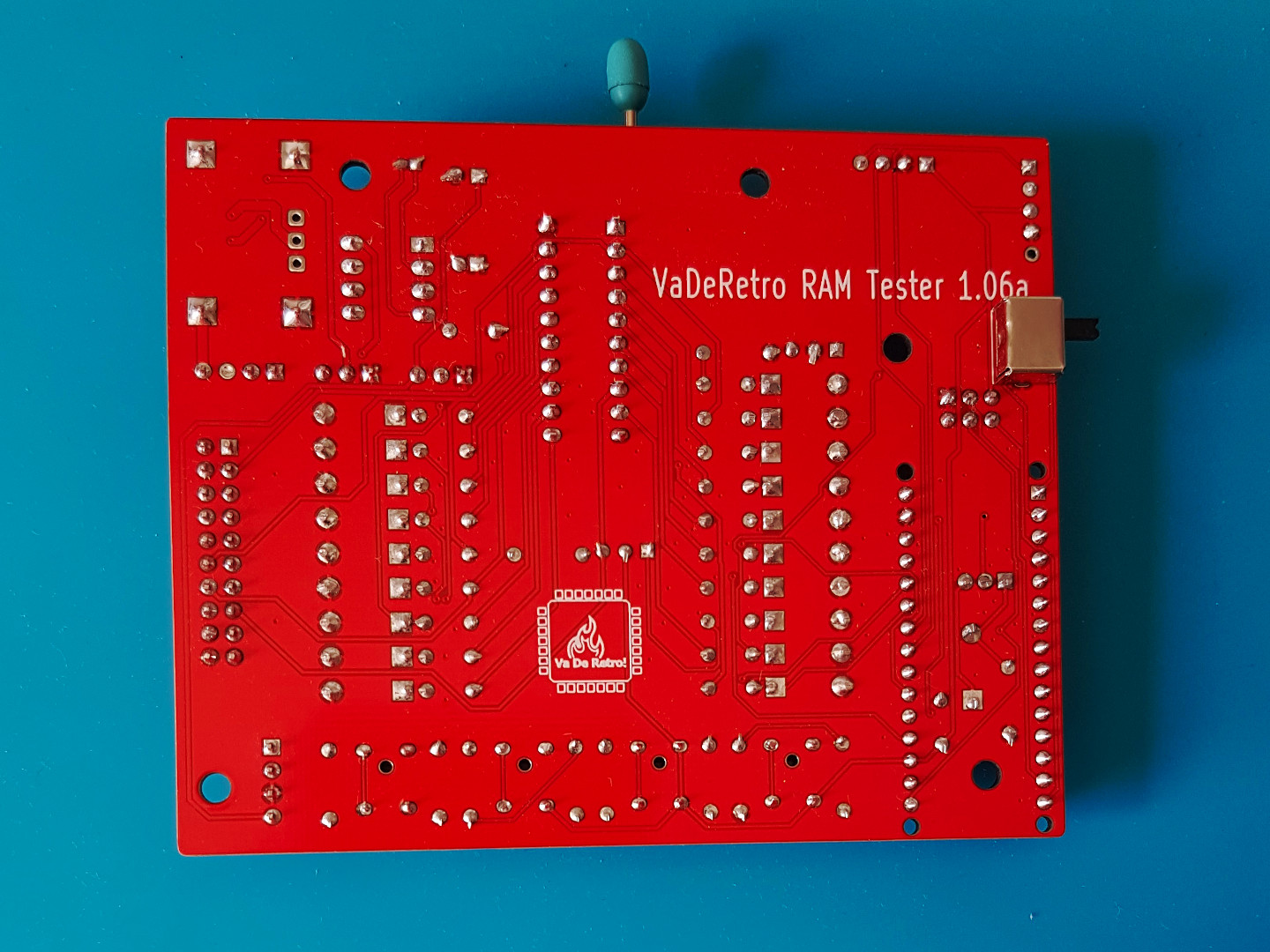

16) Vista de la cara inferior de la placa después de ser limpiada con alcohol isopropílico y un cepillo (p.e. uno de dientes) para eliminar los restos de flux.

17) Instalamos el LMC7660 (U3) en su zócalo y procedemos a ubicar en sus respectivos agujeros los tornillos (S1) y espaciadores M3 (S2). Bajo el área de la pantalla OLED, en las cercanías de J1', el espaciador M3 de 10mm. (S2) queda, como todos los demás, en la cara inferior de la placa. A él atornillamos el espaciador M3 de 8mm. con rosca (S3) y sobre este último va el último tornillo (S1) que ajustaremos para que sirva de soporte a la pantalla OLED.

Colocamos los puentes para J2 (pines 1-2), para JP6 (EXT, pines 1-2) y para JP5 (los dos pines más a la derecha).

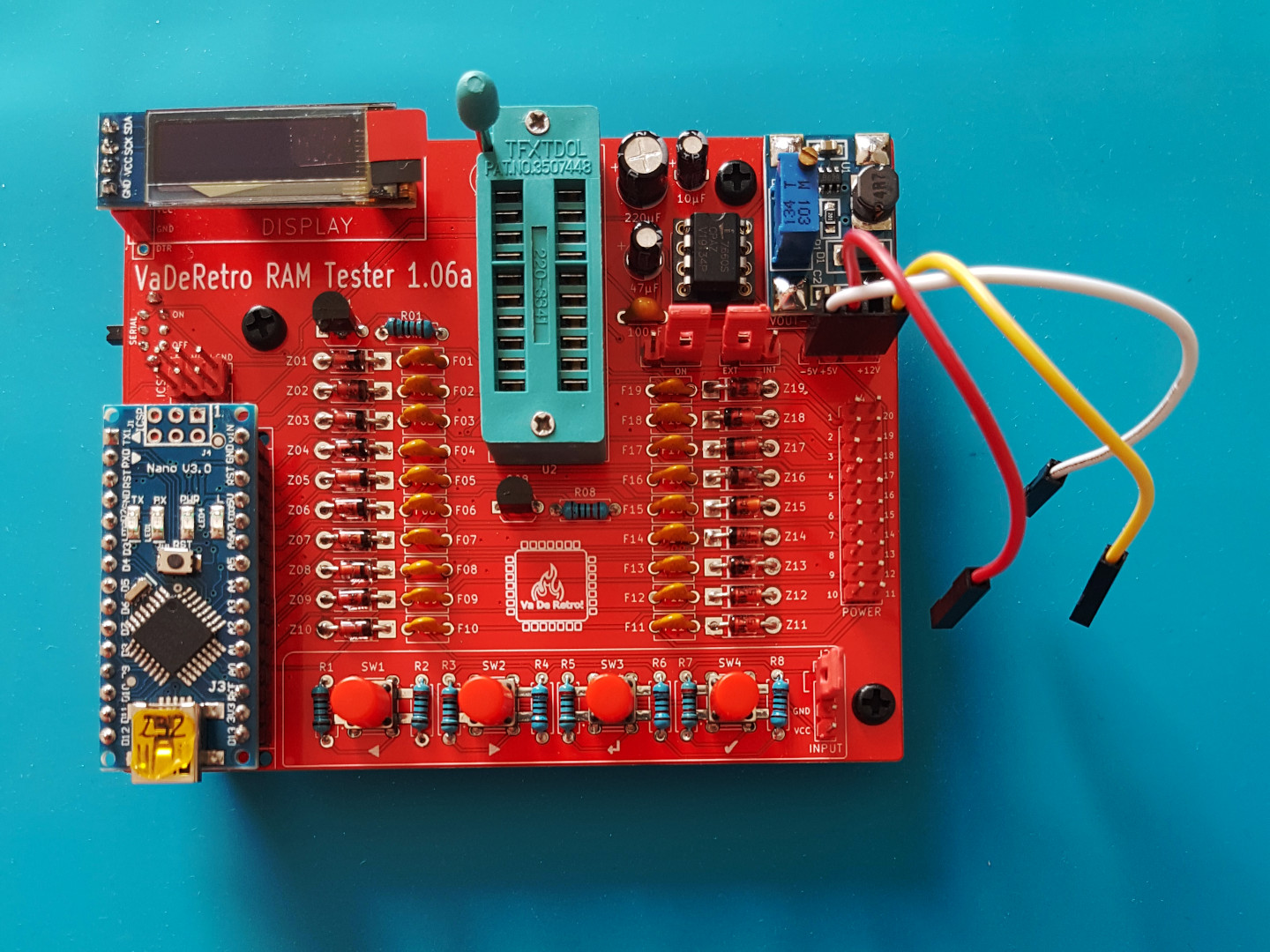

18) Añadimos las tapas rojas a cada uno de los pulsadores, instalamos la pantalla OLED y el Nano en sus respectivos zócalos y, una vez conectado el juego de cables J3' en J3, el aspecto final debe ser muy parecido a éste.

Nota: Un orden de montaje alternativo sería:

- Resistencias de 330Ω

- Resistencias de 10kΩ

- Resistencias de 20kΩ

- Diodos zener

- MOSFET IRFU5410

- Fusible PPTC 6V 250mA

- Fusibles PPTC 6V 30mA

- Condensadores de 100nF

- Zócalo DIP-8

- MOSFET BS250 y 2N7000

- Pulsadores de la botonera

- Condensadores electrolíticos por orden de altura

- Tiras de pines

- Zócalo ZIF

- Módulo HW-668

- Limpieza del flux de la cara inferior

- Conmutador SERIAL (SW0)

- Limpieza del flux de la cara superior (SW0 e IRFU5410)