Va de Retro DRAM tester [v2.00]

Moderadores: cacharreo, Fundadores

Reglas del Foro

Aquí solo tienen cabida proyectos de hardware que incluyan siempre al menos sus esquemáticos para poder reproducirlos si llevan componentes electrónicos, y si es posible los ficheros del programa en que se hacen, los diseños de las placas, los gerber, etc. Si llevan algún tipo de software asociado debe estar diponible el código fuente

Para los que no cumplen estas condiciones se debe postear en el foro de proyectos generales.

Aquí solo tienen cabida proyectos de hardware que incluyan siempre al menos sus esquemáticos para poder reproducirlos si llevan componentes electrónicos, y si es posible los ficheros del programa en que se hacen, los diseños de las placas, los gerber, etc. Si llevan algún tipo de software asociado debe estar diponible el código fuente

Para los que no cumplen estas condiciones se debe postear en el foro de proyectos generales.

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

La interfaz está completa al 100%. Ahora queda revisar los tests en sí, hacer algunas pruebas internas y cuando estén ajustados los tiempos a niveles aceptables, publicar el firmware por aquí.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Sobre placa v1.05c,

ya está confirmado que está funcionando así que, los que no lo hayáis hecho aún, podéis montarla cuando os guste. Algunos me habéis comentado que vais a montarla inicialmente sin los zeners, probarla en modo continuo y cuando se vea que va bien, ir soldando uno por uno y repitiendo tests para localizar los que pudieran estar medio cascados (alta capacitancia). Me parece buena idea y es más sencillo así, que soldar todos y después ir soltándole el pin a tierra.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

Firmware fw0.22

Firmware fw0.22

Binarios

- Logo

- Selección de chip (asegurarse de que el zócalo ZIF está vacío y no hay cables en J4)

- Información sobre el cableado de tensiones ("wiring") entre J3 y J4 (se debe fijar como se indica y, una vez hecho y verificado, colocar el chip en el zócalo ZIF)

- Hay dos modos dependiendo de si se pulsa el botón OK(✓) con:

- Test de pines (Pin test en el que el usuario puede utilizar J3 y un cable conectado a J2/GND (o al pin 20 del zócalo ZIF) para hacer conexiones a los pines 1-19 de J4 y comprobar su lectura en la pantalla, se acaba al pulsar simultáneamente UP(◀) y OK(✓))

- Autodiagnóstico (Self-test), diagnóstico de las conexiones (excepto en J4#9, 10 y 11) en el que solo es necesario seguir las indicaciones que el tester muestra en la esquina inferior izquierda y pulsar el botón OK(✓) para confirmar.

Notas

Binarios

- Firmware (78.3KiB)

- Logo

- Selección de chip (asegurarse de que el zócalo ZIF está vacío y no hay cables en J4)

- Información sobre el cableado de tensiones ("wiring") entre J3 y J4 (se debe fijar como se indica y, una vez hecho y verificado, colocar el chip en el zócalo ZIF)

- Hay dos modos dependiendo de si se pulsa el botón OK(✓) con:

- pulsación corta, test simple que al concluir muestra el resultado (una vez acaban las pruebas sobre la memoria se puede abandonar con el botón BACK(↲) o repetir el test pulsando el botón AGAIN (↺)),

- pulsación larga, test automático que repite una y otra vez las pruebas sobre la memoria y a través del puerto serie facilita la información sobre el número de tests pasados, fallidos y totales (cada vez que acaban las pruebas se puede abandonar dejando pulsado el botón BACK(↲)).

- Test de pines (Pin test en el que el usuario puede utilizar J3 y un cable conectado a J2/GND (o al pin 20 del zócalo ZIF) para hacer conexiones a los pines 1-19 de J4 y comprobar su lectura en la pantalla, se acaba al pulsar simultáneamente UP(◀) y OK(✓))

- Autodiagnóstico (Self-test), diagnóstico de las conexiones (excepto en J4#9, 10 y 11) en el que solo es necesario seguir las indicaciones que el tester muestra en la esquina inferior izquierda y pulsar el botón OK(✓) para confirmar.

Notas

- Esta versión no muestra la demo y no tiene test de botonera,...

- Para actualizar el firmware o ejecutar cualquiera de los tests siempre hay que tener la precaución de no tener cables en J4 y el zócalo ZIF sin chip (vacío) pues en caso contrario puede producirse un error de comunicación con el Nano.

- No existe aún una verificación de las tensiones en J4 por lo que es importante asegurarse de que el cableado de J3 a J4 es correcto antes de colocar el chip en el zócalo ZIF pues, de otro modo, podría dañarse la memoria.

- Para comprobar el tester y/o sus modificaciones se recomienda utilizar la versión del firmware fw0.19.

© cacharreo

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Para el autodiagnóstico (self-test) es necesario instalar dos cables en los pines 1 y 2 del Nano (los de las pinzas amarillas en la foto con los cables naranja y verde) que, siguiendo las indicaciones en pantalla, se irán conectando a J4.

el test se realiza en dos rondas, la primera usando el pin 1 del Nano y la segunda con el pin 2 y, para ganar en velocidad, simplifica automáticamente las pruebas fallidas en la segunda ronda.

Es una primera versión y es más que previsible que necesite más ajustes después de comprobar los resultados reales en los testers que pudieran tener problemas.

el test se realiza en dos rondas, la primera usando el pin 1 del Nano y la segunda con el pin 2 y, para ganar en velocidad, simplifica automáticamente las pruebas fallidas en la segunda ronda.

Es una primera versión y es más que previsible que necesite más ajustes después de comprobar los resultados reales en los testers que pudieran tener problemas.

© cacharreo

-

geloalex

- Demonio segundo orden

- Mensajes: 1431

- Registrado: 19 Abr 2018, 19:21

- Ubicación: Instagram: geloalex

- Has thanked: 964 times

- Been thanked: 502 times

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Nuevo firma cargado y lleva algo mas de 500 test si fallar sobre 4164 buena...

Parece como si afinases "algo" en los anteriores test con el firm anterior tenia algun fallo esporádico enn el teclado , asi como en algun test ...4 fallos sobre 800.

Puede que lo poco que lo manipulé , lo que interfería hora ya no

Parece como si afinases "algo" en los anteriores test con el firm anterior tenia algun fallo esporádico enn el teclado , asi como en algun test ...4 fallos sobre 800.

Puede que lo poco que lo manipulé , lo que interfería hora ya no

SpectrumZX81,ZX48,ZX48+,ZX128+2+3CommodoreA1200,A500,C64,C64C,C16AmstradCPC464,CPC6128MSXHB20P,HB75P,HBF1,HBF1XD,SVI728,8020Atari2600Sixer,2600Jr,7800PhillipsVideopacG7000NintendoGB,GBC,GBA,NES,FAMICOM,SNES,N64PCEnginePCEngine,PCEngineDUOSegaGG,SMS,SMS2,MD1,MD2,MEGACD2,SATURN,DC,NAOMIMicrosoftXBOX360Sony PS1,PS2,PS3,PS4,PSP,PSVitaMINISNES,SNES,MD,PSX INSTAGRAM: geloalex

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Perfecto entonces. ¿Has llegado a probar el self-test?

© cacharreo

-

geloalex

- Demonio segundo orden

- Mensajes: 1431

- Registrado: 19 Abr 2018, 19:21

- Ubicación: Instagram: geloalex

- Has thanked: 964 times

- Been thanked: 502 times

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Aun no , tengo el taller leonera total.

780 test OK

Edito: mas de 1300 test OK

780 test OK

Edito: mas de 1300 test OK

SpectrumZX81,ZX48,ZX48+,ZX128+2+3CommodoreA1200,A500,C64,C64C,C16AmstradCPC464,CPC6128MSXHB20P,HB75P,HBF1,HBF1XD,SVI728,8020Atari2600Sixer,2600Jr,7800PhillipsVideopacG7000NintendoGB,GBC,GBA,NES,FAMICOM,SNES,N64PCEnginePCEngine,PCEngineDUOSegaGG,SMS,SMS2,MD1,MD2,MEGACD2,SATURN,DC,NAOMIMicrosoftXBOX360Sony PS1,PS2,PS3,PS4,PSP,PSVitaMINISNES,SNES,MD,PSX INSTAGRAM: geloalex

-

cacharreo

- Moderador

- Mensajes: 6283

- Registrado: 09 Ago 2019, 10:17

- Ubicación: /home/cacharreo/

- Has thanked: 1278 times

- Been thanked: 3092 times

- Contactar:

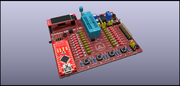

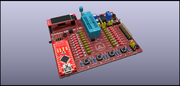

Versión 1.06a, esquemas, materiales y placa

Versión 1.06a

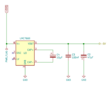

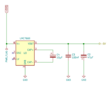

RAM tester

Módulo de protección de pines

Módulo de protección para el pin 1

Módulo de protección para el pin 8

Módulo convertidor DC-DC +5V-5V

Módulo convertidor DC-DC HW-668

Módulo de entrada (botonera)

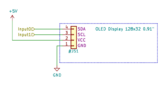

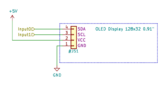

Módulo de salida (pantalla OLED 0.91"/0.96"/1.3") ⁽¹⁾

Notas para el ensamblaje

- Se aconseja decidir de entrada si se va a utilizar o no un módulo HW-668.

- En caso negativo es muy recomendable montar (e incluso probar) el step-up DC-DC antes que el resto de componentes.

- Confirmar el sentido del diodo D31 antes de montar.

- Intentar soldar U31 a un máximo de 300ºC/10s.

Lista de componentes (113)

Lista de componentes del módulo HW-668 (ya incluida en la anterior)

Lista de componentes interactiva

Gerbers

Descargar

PCB

⁽¹⁾ Especial atención a las pantallas, deben ser II2 o I²C (algunas vienen sin interfaz, otras con 7 pines para SPI) y, por la buena salud de la pantalla y del tester, los 4 pines deben seguir el orden de J1 o J1'.

⁽²⁾ La altura del vástago en los botones debe ser diferente si se pretende montar el tester en una carcasa y estos quedan en la placa. Si se van a usar botones de panel, en la placa se sueldan los 2 pines inferiores en el lugar de cada botón.

⁽³⁾ Se pueden usar en su lugar pines DuPont hembra y macho convencionales pero el Arduino Nano quedará bastante más alto.

⁽⁴⁾ NANO v3 con ATmega328P a 16MHz, FTDI FT232RL, gestor de arranque "nuevo" (optiboot) y pines redondos.

⁽⁵⁾ Blanco, rojo y amarillo respectivamente.

⁽⁶⁾ DuPont Blocking Pin / AMP-LATCH Keying Plug TE 499712-1 / Harwin M20-003 Polarising Pin.

RAM tester

Módulo de protección de pines

Módulo de protección para el pin 1

Módulo de protección para el pin 8

Módulo convertidor DC-DC +5V-5V

Módulo convertidor DC-DC HW-668

Módulo de entrada (botonera)

Módulo de salida (pantalla OLED 0.91"/0.96"/1.3") ⁽¹⁾

Notas para el ensamblaje

- Se aconseja decidir de entrada si se va a utilizar o no un módulo HW-668.

- En caso negativo es muy recomendable montar (e incluso probar) el step-up DC-DC antes que el resto de componentes.

- Confirmar el sentido del diodo D31 antes de montar.

- Intentar soldar U31 a un máximo de 300ºC/10s.

Lista de componentes (113)

| Cantidad | Referencia | Valor |

|---|---|---|

| 1 | U31 | SX1308 SMD SOT-23-6 (opcional HW-668) |

| 1 | R31 | 200Ω 1/8W 1% SMD 0805 (opcional HW-668) |

| 2 | C31,C32 | 18µF 50V SMD 0805 (opcional HW-668) |

| 1 | D31 | SS34 Rectificador Schottky 40V 3A SMD SMA (opcional HW-668) |

| 1 | R0 | 330Ω 1/4W 1% |

| 5 | R4,R6,R8,R01,R08 | 10kΩ 1/4W 1% |

| 5 | R1,R2,R3,R5,R7 | 20kΩ 1/4W 1% |

| 20 | Z0,Z01,Z02,Z03,Z04,Z05,Z06,Z07,Z08,Z09,Z10, | 1N4733A 5.1V 1W |

| Z11,Z12,Z13,Z14,Z15,Z16,Z17,Z18,Z19 | ||

| 1 | F0 | Fusible rearmable PPTC 6V 250mA |

| 19 | F01,F02,F03,F04,F05,F06,F07,F08,F09,F10, | Fusible rearmable PPTC 6V 30mA |

| F11,F12,F13,F14,F15,F16,F17,F18,F19 | ||

| 1 | C3 | 100nF 25V MLCC |

| 1 | Q0 | IRFU5410 TO-251-3 |

| 1 | Q01 | BS250 TO-92-3 |

| 1 | Q08 | 2N7000 TO-92-3 |

| 1 | U3 | Zócalo de agujero redondo DIP-8 |

| 1 | C4 | 10µF 25V 4x7mm electrolítico ó A106 10V SMD tántalo (EIA-3216/10) |

| 1 | L31 | 4.7µH SMD LQ55DN (opcional HW-668) |

| 4 | SW1,SW2,SW3,SW4 | ◀,▶,↲,✓ (push tactile switches SPST 6x6x4.3mm ó C&K TLSMDT3C020GLFS) ⁽²⁾ |

| 1 | J0 | ICSP Pines macho 2x03 2.54mm (opcional) |

| 1 | J1 | I2C/OUTPUT Pines hembra 1x05 2.54mm |

| 1 | J1' | I2C Pines hembra 1x04 2.54mm (opcional) |

| 1 | J2 | INPUT Pines macho 1x04 2.54mm |

| 1 | J3 | POWER_RAIL Pines macho 1x04 2.54mm |

| 1 | J3' | POWER_RAIL Housing DuPont hembra 1x04 𝄩2.54mm (con el penúltimo pin bloqueado) |

| 1 | J4 | POWER Pines macho 2x10 2.54mm |

| 1 | JP5 | CTRL5 Pines macho 1x02 2.54mm |

| 1 | JP6 | CTRL12 Pines macho 1x03 2.54mm |

| 2 | J5 | Pines hembra de agujero redondo 1x15 2.54mm (para zócalo del Nano) |

| 2 | J5' | Pines macho de agujero redondo 1x15 2.54mm (para el Nano) ⁽³⁾ |

| 4 | J6,J7,J8,J9 | VIN+,VIN-,VOUT+,VOUT- Pin de latón 1.00mm (para fijar el módulo HW-668) |

| 1 | C2 | 47µF 25V 5x11mm electrolítico ó A476 10V SMD tántalo (EIA-3216/10) |

| 1 | C1 | 220µF 25V 6.3x11.5mm electrolítico ó B227 10V SMD tántalo (EIA-3528) |

| 1 | SW0 | Conmutador DPDT SK-22D07 (opcional) |

| 1 | U2 | ZIF socket 20pos |

| 1 | U3 | LMC7660 (montado sobre zócalo U3) |

| 1 | HW-668 | Módulo compacto HW-668 (opcional) |

| 1 | RV31 | Trimmer 10kΩ Bourns/Baoter 3/8" 3296W-1 (opcional HW-668) |

| 1 | U1 | Nano (montado sobre zócalo J5) ⁽⁴⁾ |

| 1 | J1 | Pantalla OLED 0.91" I2C 128x32 píxeles amarilla, azul o blanca (sobre J1) (opción) |

| 1 | J1' | Pantalla OLED 0.96"/1.3" I2C 128x64 píxeles amarilla, azul o blanca (sobre J1') (opción) |

| 1 | JP2' | Puente cerrado de 2 pines 2.54mm para habilitar los botones en INPUT |

| 1 | JP5' | Puente cerrado de 2 pines 2.54mm para habilitar en JP5 los +5V en J3, J4, el zócalo ZIF y los conversores DC-DC |

| 1 | JP6' | Puente cerrado de 2 pines 2.54mm para conmutar en JP6 entre el módulo DC-DC HW-668 interno o externo |

| 3 | W1,W2,W3 | Cables DuPont F-F 10cm para puentes entre POWER y -5V,+5V y +12V ⁽⁵⁾ |

| 1 | PCB | Placa VaDeRetro RAM Tester |

| 5 | S1 | Tornillo de nylon M3 6mm negro |

| 5 | S2 | Espaciador de nylon M3 10mm negro |

| 1 | S3 | Espaciador de nylon M3 8mm con rosca de 6mm negro |

| 1 | J3/3 | Pin de bloqueo ⁽⁶⁾ |

| Cantidad | Referencia | Valor | Formato |

|---|---|---|---|

| 1 | R31 | 200Ω 1/8W 1% | 0805 |

| 2 | C31,C32 | 18µF 50V | 0805 |

| 1 | U31 | SX1308 | SOT-23-6 |

| 1 | D31 | SS34 Rectificador Schottky 40V 3A | SMA |

| 1 | L31 | 4.7µH | LQ55DN |

| 1 | RV31 | Trimmer 10kΩ Bourns/Baoter 3/8" 3296W-1 | 0.375" Trimpot 3 pins |

Gerbers

Descargar

PCB

⁽¹⁾ Especial atención a las pantallas, deben ser II2 o I²C (algunas vienen sin interfaz, otras con 7 pines para SPI) y, por la buena salud de la pantalla y del tester, los 4 pines deben seguir el orden de J1 o J1'.

⁽²⁾ La altura del vástago en los botones debe ser diferente si se pretende montar el tester en una carcasa y estos quedan en la placa. Si se van a usar botones de panel, en la placa se sueldan los 2 pines inferiores en el lugar de cada botón.

⁽³⁾ Se pueden usar en su lugar pines DuPont hembra y macho convencionales pero el Arduino Nano quedará bastante más alto.

⁽⁴⁾ NANO v3 con ATmega328P a 16MHz, FTDI FT232RL, gestor de arranque "nuevo" (optiboot) y pines redondos.

⁽⁵⁾ Blanco, rojo y amarillo respectivamente.

⁽⁶⁾ DuPont Blocking Pin / AMP-LATCH Keying Plug TE 499712-1 / Harwin M20-003 Polarising Pin.

© cacharreo

-

Gomas48K

- Aspirante a demonio

- Mensajes: 277

- Registrado: 16 Jun 2021, 06:08

- Ubicación: España

- Has thanked: 727 times

- Been thanked: 221 times

Re: Versión 1.06, esquemas, materiales y placa

Wow!!! Sorpresa!!!

Gran trabajo como siempre!!!

Con mi Gomas 48K, hasta el mismo infierno!!!

-

geloalex

- Demonio segundo orden

- Mensajes: 1431

- Registrado: 19 Abr 2018, 19:21

- Ubicación: Instagram: geloalex

- Has thanked: 964 times

- Been thanked: 502 times

Re: Test de Memorias 4116, 4164 y 41464 [beta testing]

Bueno, como vamos con las nuevas placas V1.05C , están montadas ya??? no se oye nada por aquí

SpectrumZX81,ZX48,ZX48+,ZX128+2+3CommodoreA1200,A500,C64,C64C,C16AmstradCPC464,CPC6128MSXHB20P,HB75P,HBF1,HBF1XD,SVI728,8020Atari2600Sixer,2600Jr,7800PhillipsVideopacG7000NintendoGB,GBC,GBA,NES,FAMICOM,SNES,N64PCEnginePCEngine,PCEngineDUOSegaGG,SMS,SMS2,MD1,MD2,MEGACD2,SATURN,DC,NAOMIMicrosoftXBOX360Sony PS1,PS2,PS3,PS4,PSP,PSVitaMINISNES,SNES,MD,PSX INSTAGRAM: geloalex