Supongamos que una o a ambas de estas placas 1.5x quisieramos añadirle un lector de tarjetas adicional con el propósito de que admitieran los dos tipos de tarjeta, SD y TF (es decir, microSD).

El lector TF del que disponemos no admite la detección de la tarjeta (cuando está o cuando no está introducida) pero afortunadamente sí que lo admite el lector SD.

Añadir un segundo lector a una de las placas, podría hacerse con dos diferentes enfoques

1) tal cual y conectando sus pines a los correspondientes del lector preexistente, o

2) de forma que el lector TF quedara deshabilitado cuando hubiera una tarjeta introducida en el lector SD (esto impide problemas si por error se introduce una tarjeta en cada lector).

Veamos cómo se podría implementar esta segunda opción de una forma sencilla.

Partimos de que la detección de la tarjeta tiene un funcionamiento muy simple. Cuando hay una tarjeta dentro, el pin de detección de tarjeta se conecta a tierra.

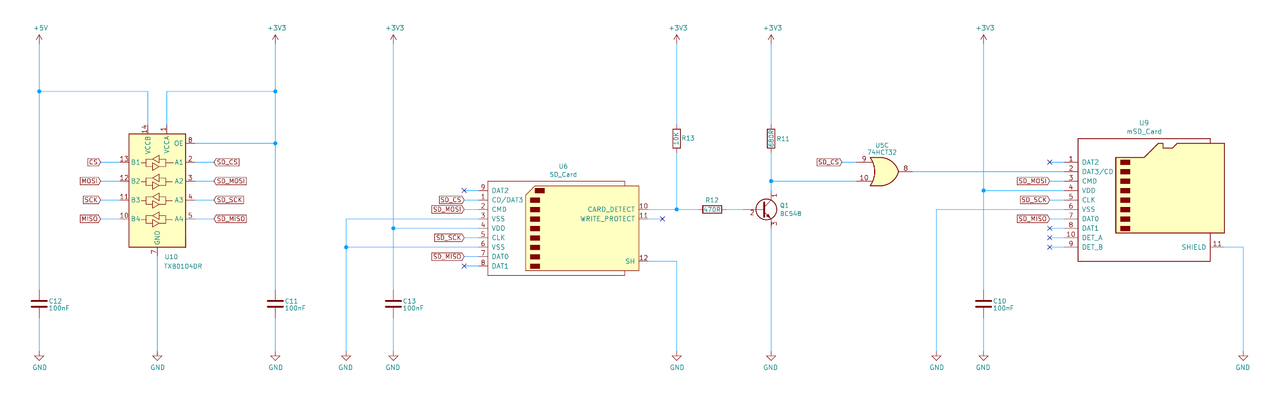

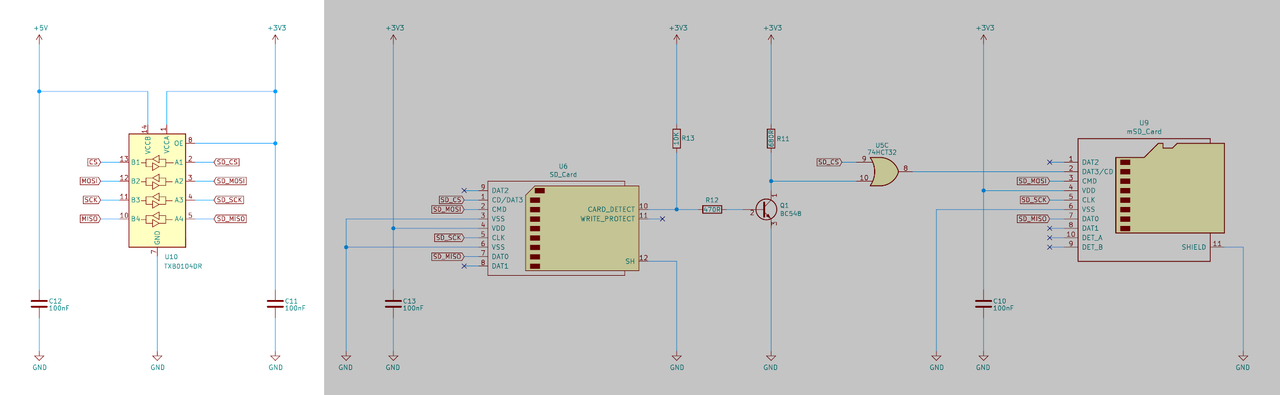

En ambos lectores de tarjetas habrá que conectar una señal CS (

Chip Select) que indica

(1) a la tarjeta que está activa cuando esta señal está a un nivel lógico bajo o que está desactivada cuando dicha señal está a un nivel lógico alto.

Independientemente del lector de tarjetas, la señal CS proviene del microcontrolador ATmega328P pero, como no se podría conectar directamente al lector

(2), utilizamos la señal SD_CS que es la misma señal una vez transformada por el conversor de niveles.

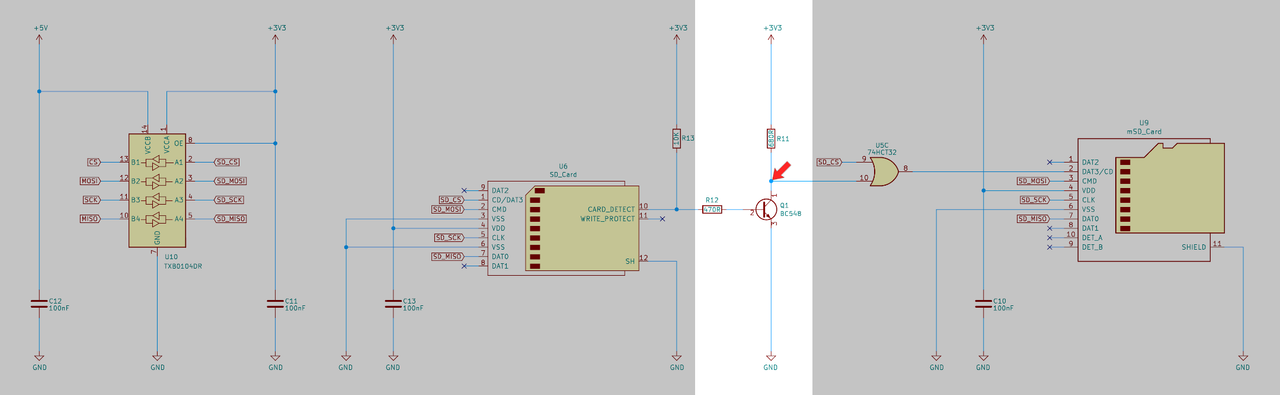

Como hemos dicho, la idea es deshabilitar el lector de tarjetas TF siempre que haya una tarjeta introducida en el lector SD. Llamando CD (

Card Detect) a una variable lógica que tome el valor 0 cuando hay una tarjeta en el lector SD y tome el valor 1 cuando no, necesitamos una función lógica de CD y SD_CS que genere la señal CS para el lector TF. La tabla de verdad para dicha función, f(CD, SD_CS) sería la siguiente:

| CD | SD_CS | f(CD, SD_CS) |

|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

es decir, esta función lógica toma el valor 0 si y solo si CD está a nivel lógico alto y SD_CS está a nivel lógico bajo.

Nuestra función podría escribirse como

f(CD, SD_CS) = !(CD * !SD_CS)

que podría implementarse electrónicamente con una puerta NAND y un inversor,

(pulsar el botón Run/Stop y hacer click sobre los valores de entrada, a la izquierda del circuito, para comprobar los valores de salida, a la derecha)

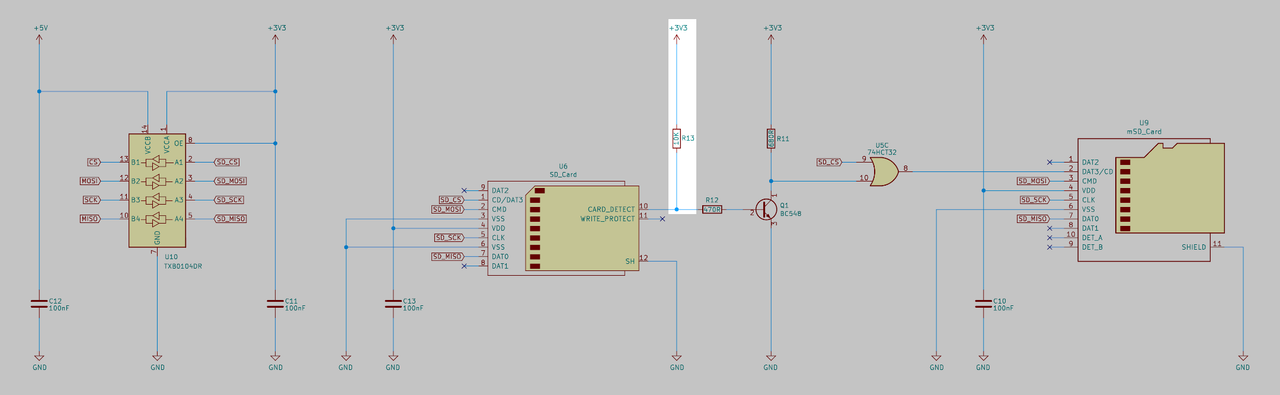

pero como en el esquema del ZX DD MTD 1.5x no utilizamos puertas NAND y sí que nos sobran puertas OR, podríamos reescribir la función utilizando su forma alternativa:

f(CD, SD_CS) = !CD + SD_CS

que se implementaría del siguiente modo,

(pulsar el botón Run/Stop y hacer click sobre los valores de entrada, a la izquierda del circuito, para comprobar los valores de salida, a la derecha)

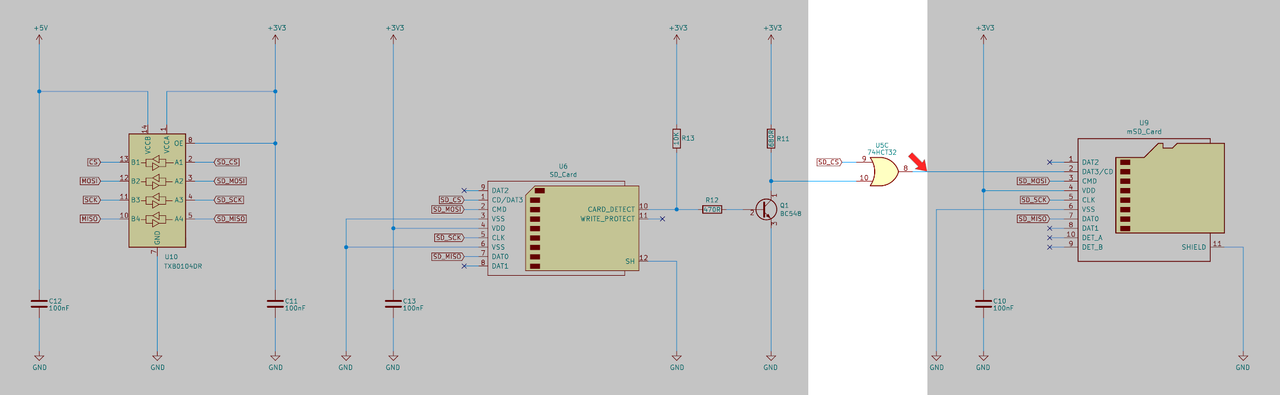

Utilizando componentes discretos a fin de no añadir más puertas lógicas, quedaría el siguiente circuito.

(pulsar el botón Run/Stop y hacer click sobre los valores de entrada, a la izquierda del circuito, para comprobar los valores de salida, a la derecha)

que es lo que pretendíamos conseguir. Ya solo queda añadir a los respectivos esquemas las tres nuevas resistencias y el transistor NPN universal (p.e. cualquier BC548) que lleva menos de cinco minutos.

(1) suponiendo que CS queda habilitada a nivel bajo (

active low)

(2) La señal CS tiene niveles TTL (0-5V) y para el lector de tarjetas necesitamos niveles CMOS (0-3.3V)