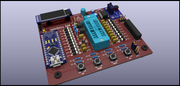

Modificaciones sobre los prototipos v1.02 (obteniendo como resultado una placa v1.02c)

¡No conectar la alimentación a la placa hasta completar las modificaciones!

Nota sobre los botones: ¡¡¡PELIGRO!!!

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.

La estrategia recomendada es realizar los cortes en las pistas antes de soldar componentes, después soldarlos, lavar la placa con alcohol isopropílico para eliminar los restos de

flux y entonces soldar los cables como se indica a continuación.

1.

Sobre condensadores C1 y C4

1.1. En esta versión la huella en la placa para estos dos componentes es para un condensador de disco (de lenteja).

1.2. Si se van a utilizar condensadores MLCC es conveniente usar los de patillas

kinked o adaptarle sus patillas a esa forma con un alicate fino.

2.

Mejoras en la generación de los -5V (opcional, previsiblemente todo funcionará bien sin esta modificación aunque los -5V no estarán tan clavados)

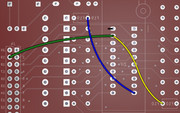

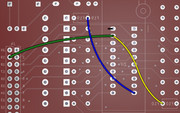

2.1. En la cara superior de la placa practicar un corte en las 2 pistas marcadas con las X azules,

2.2. en la esquina SW del pad de VIN+,

2.3. en la cara inferior de la placa, otro corte

2.4. en la esquina NE del pad del pin 8 de U3.

2.5. Por la cara inferior soldar 2 puentes como los señalados en color amarillo,

2.6. del pad de VIN+ al pad del cátodo de D1,

2.7. del pad del pin 8 de U3 al ánodo de D1.

3.

Reorganización de señales para adaptarlas al nuevo firmware

3.1. En la cara superior de la placa practicar un corte en las 3 pistas marcadas con las X azules,

3.2. en la esquina SW del pad izquierdo de F19,

3.3. en la esquina SE del pad izquierdo de F19,

3.4. al E del pad derecho de F10,

3.5. Por la cara inferior soldar 4 puentes como los señalados en colores azul, amarillo, negro y verde,

3.6. del pad de F19 más cercano al zócalo ZIF al pin 10 del zócalo ZIF,

3.7. del pad de F10 más cercano al zócalo ZIF al pin 19 del zócalo ZIF,

3.8. del pin 19 de J4 al pin 19 del zócalo ZIF.

3.9. del pin 20 del zócalo ZIF al plano de tierra (antes rascar un círculo en el plano de tierra para crear la superficie de soldadura).

4.

Cambio en los fusibles F01 y F08 (imprescindible para memorias 4116, las demás irán bien sin esta modificación)

4.1. Adaptación a la placa v1.05

4.1.1. No soldar directamente los fusibles F01 ni F08 y soldar en cada uno de sus pads un pin de 2.54mm.

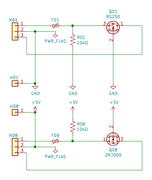

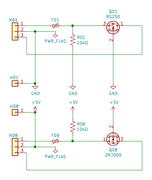

4.1.2. siguiendo este esquema

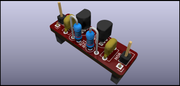

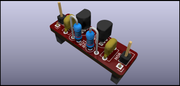

4.1.3. montar sobre una placa de prototipo (

perfboard) o una de fabricación casera, los fusibles, el conmutador y un par de conectores de pines hembra 1x03 de 2.54mm. en esta configuración,

4.1.4. que encajará en la placa v1.02 desde arriba casi como un guante (la diferencia de medidas entre pines es de 0.08mm.) Esta plaquita convierte la v1.02 al 100% a la placa v1.05.

4.1.5. H01 queda alineado con Z01-F01 y H08 con Z08-F08,

4.1.6. H01 debe conectarse a J2/3 (GND) y

4.1.7. H08 debe conectarse a J2/4 (VCC).

5.

Protección extra para prevenir cortocircuitos durante el montaje (placa 1.02d)

5.1. Seguir las instrucciones en

este enlace.

- Gerbers panelizados en matriz de 3x10 (30 placas individuales por placa de 100x100mm., 150 placas individuales con la oferta de $2 de JLCPCB, la mitad con el add-on para la conversión a v1.04, la otra mitad con el add-on para la conversión a v1.05).

Para encargar en

JLCPCB solo es necesario:

- Solicitar presupuesto (Instant quote)

- Subir el fichero .ZIP con los gerbers (Add gerber file)

- Elegir el número de placas (PCB Qty, recomendadas 5 para acceder a la oferta de $2)

- Elegir el color Rojo (PCB Color, Red)

- Abajo del todo seleccionar "Specify a location"

- En el panel derecho y bajo el botón "Save to cart", seleccionar el método de envío en la persiana desplegable

- Pulsar "Save to cart" y pagar (en caso de que se escoja la oferta de $2 y el método de envío más económico, el total es de $2 + $3.92 de portes + $0.43 de tasas, en total $6.35)

Nota sobre los botones: ¡¡¡PELIGRO!!!

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.

atención a este prototipo que lleva pulsadores SPDT, raros de encontrar, de hecho y que yo sepa hasta el año pasado ni existían (en esa configuración y tamaño), aunque se pueden utilizar pulsadores convencionales SPST cortándoles o dejando desconectado el pin NE (Noreste, o a las 2, o azimuth 45º N). De no seguir esta indicación, espérese un buen cortocircuito entre +5V y GND con consecuencias inesperadas.